# UNIVERSIDAD DE MURCIA

#### **ESCUELA INTERNACIONAL DE DOCTORADO**

Hardware Techniques for the Design of Efficient Inference Accelerators of Deep Neural Networks

Técnicas Hardware para el Diseño de Aceleradores de Inferencia Eficientes de Redes Neuronales Profundas

D. Francisco Muñoz Martínez 2022

### Universidad de Murcia Facultad de Informática

Departamento de Ingeniería y Tecnología de Computadores

## Técnicas Hardware para el Diseño de Aceleradores de Inferencia Eficientes de Redes Neuronales Profundas

Tesis Doctoral

Autor: Francisco Muñoz Martínez

Directores: Manuel Eugenio Acacio Sánchez José Luis Abellán Miguel

Murcia, Septiembre de 2022

#### Resumen

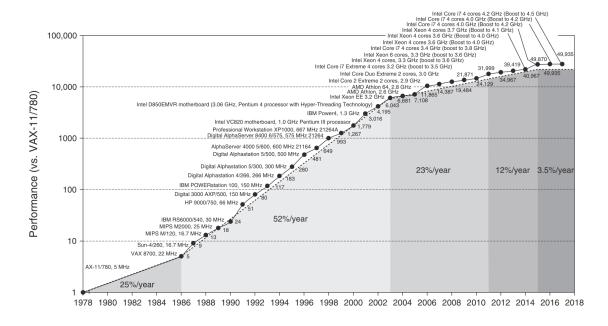

Durante los últimos 50 años, la potencia de cómputo proporcionada por los procesadores de propósito general ha experimentado un increíble incremento de rendimiento debido principalmente a la mejora de la tecnología que se utiliza para construir los chips, cumpliendo la ley empírica predicha por Gordon Moore en el año 1975 [38] que indicaba que el número de transistores en un chip se duplicaría cada dos años. Los arquitectos hardware, se han aprovechado de este hecho diseñando cauces de procesamiento cada vez más complejos o en la última década añadiendo más y más núcleos de procesamiento en un mismo chip. Desafortunadamente, debido a restricciones físicas prácticamente insuperables, el tamaño del transistor está llegando a su límite y por tanto el incremento de la potencia de cómputo está siendo comprometida, duplicándose según las tendencias actuales cada 20 años [59]. Además, este límite es alcanzado en el momento más demandante de cómputo de la historia de los computadores: la era de la inteligencia artificial, y en concreto de las redes neuronales profundas (*Deep Neural Networks* o DNNs).

Estas DNNs constituyen hoy en día un avance disruptivo para un gran número de aplicaciones de inteligencia artificial, como reconocimiento de imagen y vídeo, conducción autónoma, reconocimiento del lenguaje natural, traducción de texto, detección temprana de enfermedades, predicción meteorológica, etc. [117]. El inconveniente es que estas DNNs requieren de gran cantidad de datos y realizan millones de operaciones, demandando una masiva cantidad de cómputo, uso de memoria y energía.

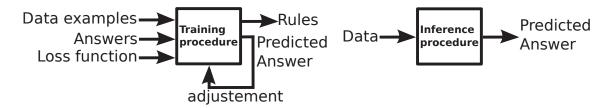

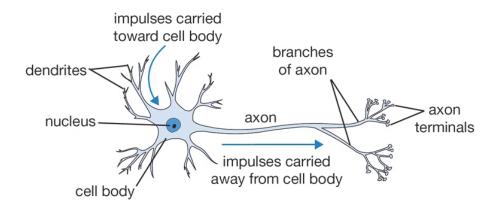

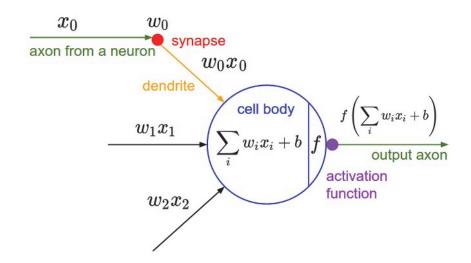

Generalmente, una DNN tiene dos fases fundamentales de operación: una primera fase de *entrenamiento*, donde un conjunto de pesos son derivados para que la DNN realice una determinada tarea, y una segunda fase de *inferencia*, donde la DNN se despliega para ser utilizada en un escenario para el cual ha sido entrenada previamente. Generalmente, la fase de entrenamiento se lleva a

cabo utilizando GPUs en grandes centros de datos [20], mientras que la fase de inferencia se suele realizar *in-situ*, en dispositivos con fuertes restricciones en cuanto a área y energía. Este hecho ha conllevado a la investigación y desarrollo de un gran número de arquitecturas aceleradoras que tratan de maximizar las demandas de eficiencia energética de estos escenarios [61], [76], [70], [31], [33].

La clave que hay detrás de todas estas arquitecturas aceleradoras ha sido capturar los diferentes patrones de datos en lo que se conoce como flujo de datos (*dataflow*) [68], y la explotación de optimizaciones arquitecturales basadas en los datos de entrada para reducir el cómputo o el movimiento de datos [33].

La primera generación de aceleradores *sistólicos* del procedimiento de inferencia para DNNs (e.g., la TPU de Google [61]) basaban su diseño en grupos (clústeres) de unidades de multiplicación y suma (unidades MACs) de tamaño fijo, interconectados mediante una red de interconexión específicamente diseñada para soportar un flujo de datos particular [23].

Desafortunadamente, con el avance y desarrollo de nuevos modelos DNNs, estos aceleradores sistólicos se han quedado obsoletos, debido principalmente a su incapacidad de adaptarse a nuevas características como: i) mayor variedad de tipos de DNNs, lo cual conlleva a mayor heterogeneidad en las demandas de cómputo; y ii) la presencia de sparsity (gran cantidad de valores cero), que viene siendo cada vez más notable en estos modelos. Explotar estas nuevas características hace que los aceleradores sistólicos compuestos por topologías *rígidas* no puedan adaptarse, traduciéndose en una baja utilización de las unidades de cómputo y en dificultad para escalar adecuadamente estas arquitecturas aceleradoras.

Con el objetivo de superar estas limitaciones, recientemente han surgido diseños de arquitecturas aceleradoras como FlexFlow [76], MAERI [70] o SIGMA [31]. Estos aceleradores utilizan topologías *flexibles* capaces de adaptar su sustrato hardware a las distintas demandas computacionales requeridas por los nuevos modelos de DNNs. Para ello, estas arquitecturas permiten configurarse para crear cualquier número de clústeres de unidades de cómputo y de cualquier tamaño, permitiendo una mejor adaptación a cualquier demanda en el mismo sustrato hardware.

Naturalmente, estas arquitecturas flexibles descritas anteriormente, aunque mejoran significativamente el aprovechamiento de las unidades de cómputo, son bastante más complejas que una simple arquitectura sistólica. Además, el número de mapeos que se pueden utilizar por cada capa es casi infinito y el espectro de evaluación y mejora del diseño hardware es mucho más amplio que en una arquitectura simple. Por este motivo, para los arquitectos de computadores es

inviable utilizar un diseño hardware directamente escrito en HDL para realizar pruebas o evaluaciones sobre el mismo.

Hasta ahora, los arquitectos de computadores han utilizado herramientas analíticas para evaluar sus diseños, empleando un conjunto de fórmulas que les permiten estimar el rendimiento y eficiencia energética en unos pocos segundos. SCALE-Sim [30], MAESTRO [68] y TimeLoop [29] han sido propuestos recientemente como ejemplos de este tipo de herramientas que permiten el análisis de diferentes flujos de datos en arquitecturas específicas para DNNs. Estas herramientas son muy potentes para explorar de forma rápida los detalles de alto nivel de la arquitectura, ya que se basan en modelos analíticos que calculan una estimación del número de ciclos de ejecución, grado de reutilización de datos y eficiencia energética mediante un conjunto de fórmulas sencillas. Este tipo de herramientas funcionan con precisión cuando se trata de arquitecturas rígidas, ya que son lo suficientemente simples como para ser representadas por un conjunto de fórmulas. Sin embargo, cuando la complejidad del acelerador crece y/o el cómputo no sigue patrones regulares, estos modelos arquitecturales no logran capturar fielmente el comportamiento exacto de la arquitectura. Esto hace, como demostramos en esta tesis, que la precisión que ofrecen estas herramientas esté muy lejos de ser óptima, ya que no son capaces de capturar detalles microarquitecturales que tienen su efecto durante las ejecuciones reales. Además, estos modelos analíticos no ejecutan realmente un modelo de DNN, por lo que no pueden utilizar los datos de entrada (por ejemplo, el número y posición de los valores cero) para evaluar optimizaciones basadas en datos.

Es necesario, por tanto, al igual que ha ocurrido anteriormente con la evaluación de diseños de CPUs [14] y GPUs [13], [115], el uso de simuladores arquitecturales con precisión a nivel de ciclo que permitan realizar cambios en el diseño de forma rápida y sencilla, y poder comprobar el efecto de dichos cambios de forma precisa.

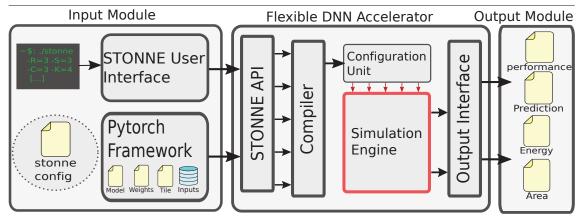

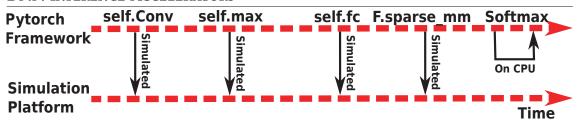

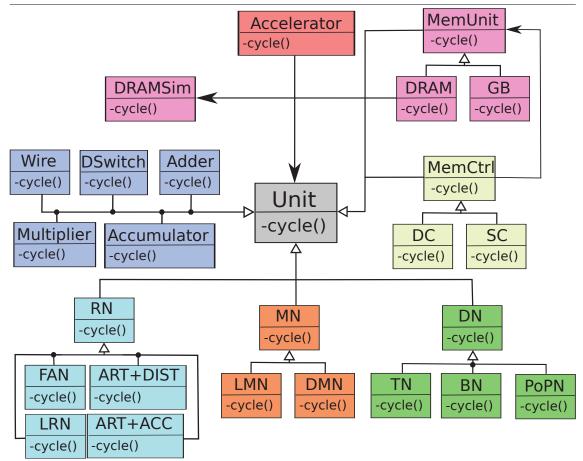

Para suplir esa demanda, como primera contribución de esta tesis diseñamos, presentamos y evaluamos el simulador STONNE (<u>Simulation TOol of Neural Network Engines</u>), un simulador microarquitectural a nivel de ciclo para aceleradores de inferencia de DNN liberado como código abierto bajo los términos de la licencia MIT. Con el objetivo de permitir evaluaciones de modelos de DNNs completos, STONNE está conectado con el conocido framework para DNNs PyTorch [5] (además de con Caffe [2]). De esta forma, STONNE puede ejecutar completamente cualquier modelo DNN denso y *sparse* soportado por el framework de DNNs que utiliza como front-end. El simulador ha sido escrito completamente en C++, siguiendo los conocidos principios de programación

GRASP y SOLID del diseño orientado a objetos [79]. Esto ha simplificado su desarrollo y facilita la implementación de cualquier tipo de módulo microarquitectural de acelerador de inferencia de DNN, mapeos de configuración flexibles o la incorporación de distintos flujos de datos.

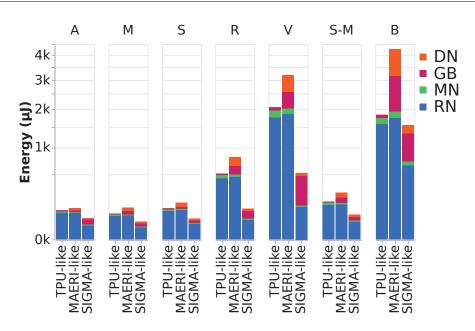

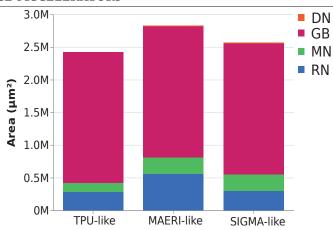

STONNE está constituido por 3 módulos principales: una plataforma de simulación que constituye el bloque principal, ya que incluye la implementación de distintos bloques hardware con el objetivo de simular de forma precisa diferentes aceleradores tanto rígidos como flexibles. Un módulo de entrada que alimenta la plataforma de simulación utilizando cualquiera de los conocidos frameworks de DNNs ya disponibles (e.g. PyTorch [5]). Finalmente, la plataforma también cuenta con un módulo de salida que se utiliza para informar sobre las estadísticas de la simulación, tales como el rendimiento, la utilización de las unidades de cómputo, y el recuento de la actividad de los diferentes componentes hardware, tales como cables, colas FIFO o el uso de la SRAM (es decir, el número de accesos). Además, utilizando estas estadísticas de actividad, este módulo de salida también informa de la cantidad de energía consumida y del área en el chip requerida por la arquitectura simulada. Para ello, STONNE emplea un modelo de área y energía basado en una tabla similar al de Accelergy [119], calculando la energía total utilizando las estadísticas de actividad a nivel de ciclo para cada módulo y una tabla particular con los diferentes costes de energía y área por operación en cada módulo. Obviamente, estas estadísticas dependen, por ejemplo, del formato particular de datos utilizado para representar los parámetros del modelo DNN (por ejemplo, fp16 o int8). Así, STONNE trae consigo diferentes tablas con costes de energía que pueden ser utilizadas por el usuario.

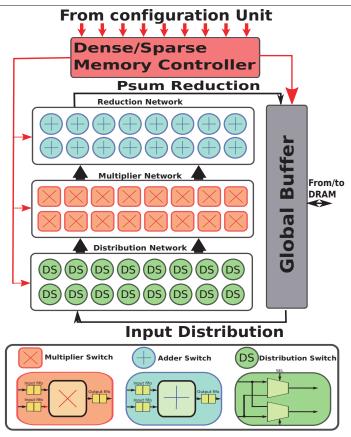

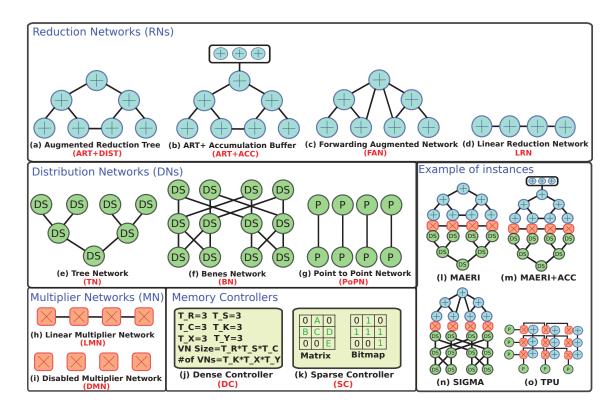

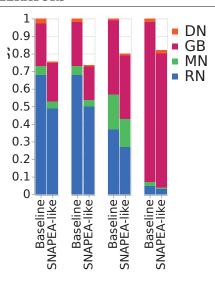

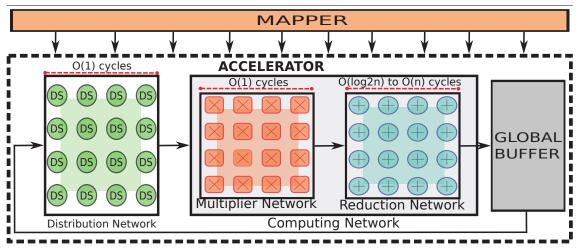

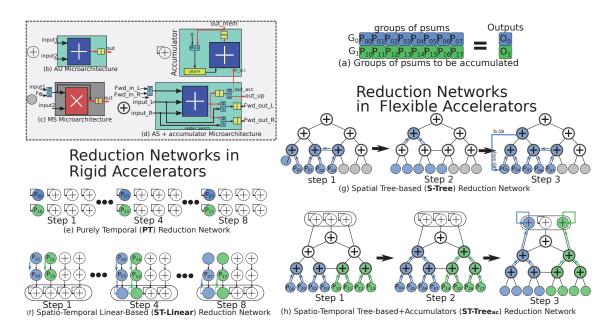

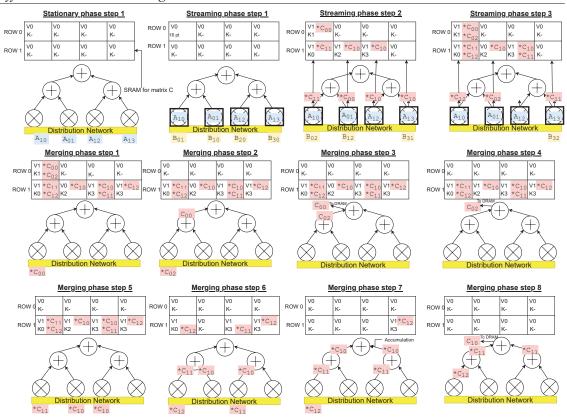

En la plataforma de simulación de STONNE todos los componentes en el chip están interconectados utilizando tres redes de interconexión: 1) Red de distribución (*Distribution Network* o DN); 2) Red de multiplicación (*Multiplier Network* o MN); y 3) Red de reducción (*Reduction Network* o RN). Esta aproximación está inspirada en la taxonomía de los flujos de comunicación en el chip de los aceleradores de DNNs [70]. Estas redes pueden ser configuradas para soportar cualquier topología con el objetivo de modelar diversas arquiteturas de acelerador, como la TPU [61], Eyeriss-v2 [24], ShiDianNao [28], SCNN [98], MAERI [70] o SIGMA [31], entre otros.

Para ello, las tres redes pueden ser organizadas para modelar cualquier acelerador mediante un flujo de datos muy sencillo. En primer lugar, para calcular todas las operaciones MAC de una determinada capa de la DNN, la DN distribuye los pesos, activaciones y sumas parciales requeridas desde una memoria SRAM (*Global Buffer* o GB) hacia la MN. Para permitir todos los tipos

de flujos de datos, la DN debe proporcionar soporte para la entrega de datos *unicast, multicast y broadcast*. Esto se consigue a través de diferentes posibles configuraciones de los conmutadores de distribución (*Distribution Switch* o DS) que integran la DN. Tras la distribución, los multiplicadores en la MN realizan las operaciones de multiplicación, generando un conjunto de sumas parciales a acumular. Finalmente, la red RN está equipada con sumadores que implementan las acumulaciones requeridas.

STONNE soporta distintas DNs como *Tree-Network, Benes-Network* o *Point-to-point network*. De forma similar, las MNs incluidas de forma nativa son la *Linear Multiplier Network* y la *Disabled Multiplier Network*. Finalmente, STONNE soporta distintas RNs para poder realizar acumulaciones de sumas parciales flexibles, lo que da soporte a distintos aceleradores. STONNE soporta una red de tipo árbol de reducción (*Reduction Tree* o RT) que denominamos árbol de reducción aumentado (ART+DIST), una red que combina ART y un *buffer* de Acumulación (ART+ACC) y una red de adelantamiento sumador (*Forwarding Adder Network* o FAN). Con el fin de soportar todos los tipos de aceleradores, en STONNE también implementamos una red de reducción lineal (*Linear Reduction Network* o LRN), que se utiliza en aceleradores rígidos como la TPU [61]. Esta red es uno de los componentes clave a la hora de desarrollar un acelerador, y nuestras contribuciones presentadas en los capítulos 3 y 4 tienen como clave el diseño de una nueva RN.

Como demostramos en el capítulo 2 de esta tesis, nuestro simulador STONNE obtiene un error de precisión con respecto al hardware real de tan solo entre el 0,14 % y el 3,10 % (1,53 % de media), demostrando que STONNE imita fielmente las características de las versiones hardware.

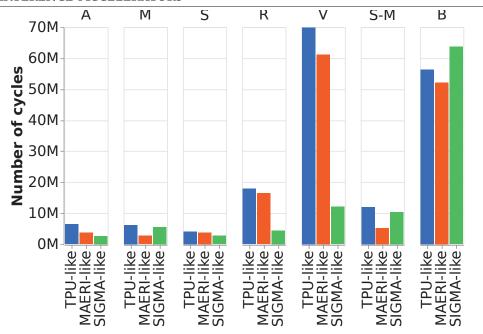

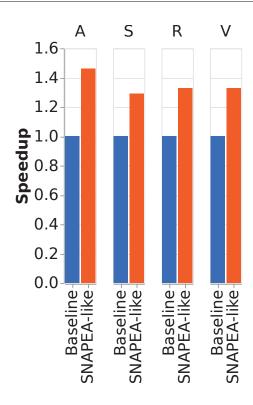

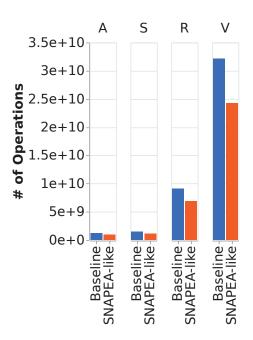

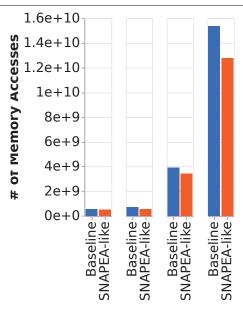

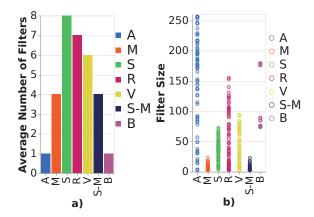

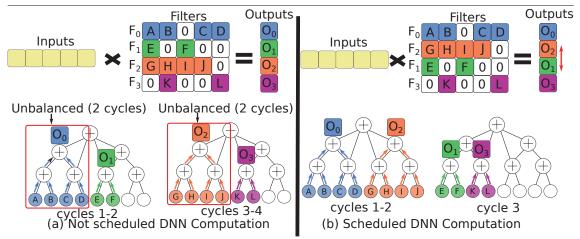

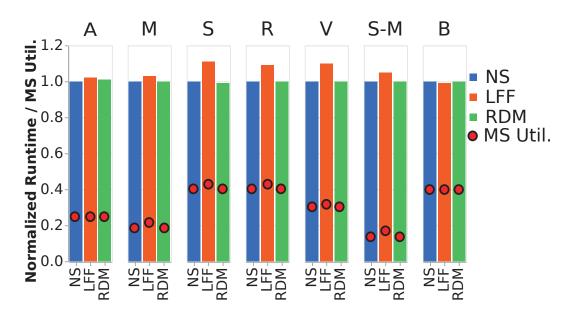

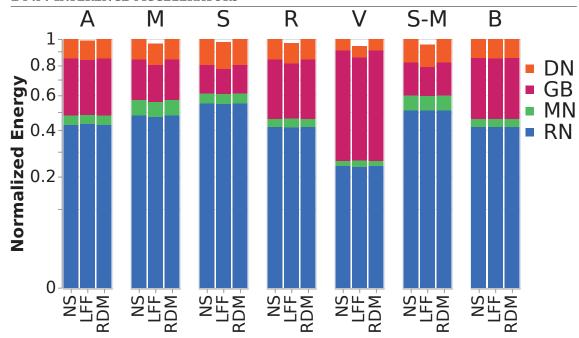

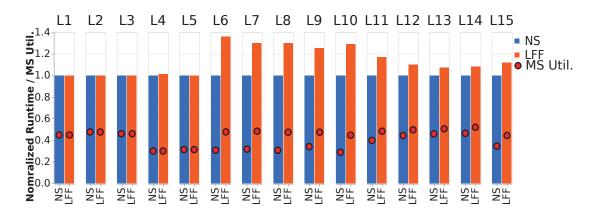

Para demostrar la usabilidad y utilidad del simulador, hemos llevado a cabo el desarrollo de tres casos de estudio. En el primer caso de estudio, hemos realizado una validación de tiempos entre los aceleradores de DNN nativamente modelados: MAERI [70], SIGMA [31] y la TPU [61]. En el segundo caso de estudio, demostramos cómo es posible modificar la plataforma de simulación de STONNE para añadir nuevos aceleradores. Para ello, modelamos el acelerador SnaPEA [33] mostrando la utilidad de STONNE para modelar aceleradores cuyas optimizaciones son dependientes de los datos de entrada. Finalmente, en el tercer caso de estudio mostramos cómo STONNE es útil para desarrollar nuevas técnicas a nivel de compilación. En concreto, en este caso de estudio mostramos que en aceleradores con soporte para *sparsity* como SIGMA [31] es primordial tener en cuenta el número de ceros que se encuentran en los filtros de una DNN y el orden en el que se ejecutan estos filtros. Ejecutar una DNN comprimida con formato

sparse sin tener en cuenta este hecho implica que la ejecución paralela de varios filtros no sea balanceada. Así, aplicar una técnica de ordenamiento de los filtros antes de la ejecución de la DNN puede tener efectos positivos significativos en el rendimiento de su procesamiento. En este caso de estudio hemos comparado tres técnicas de ordenamiento: Largest Filter First (LFF), el cual consiste en ejecutar los filtros más grandes primero, Random (RDM) y sin ordenamiento (non-scheduling o NS). Entre todos, hemos encontrado que la técnica de ordenamiento LFF es la que mejor funciona, obteniendo mejoras de rendimiento de hasta 13 % en algunas capas.

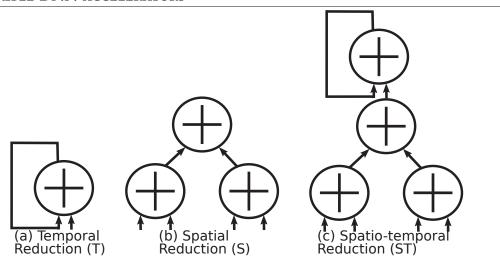

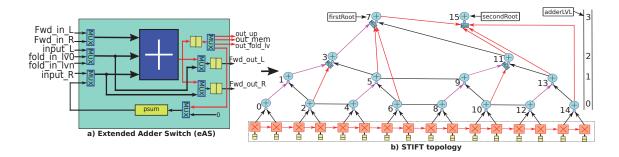

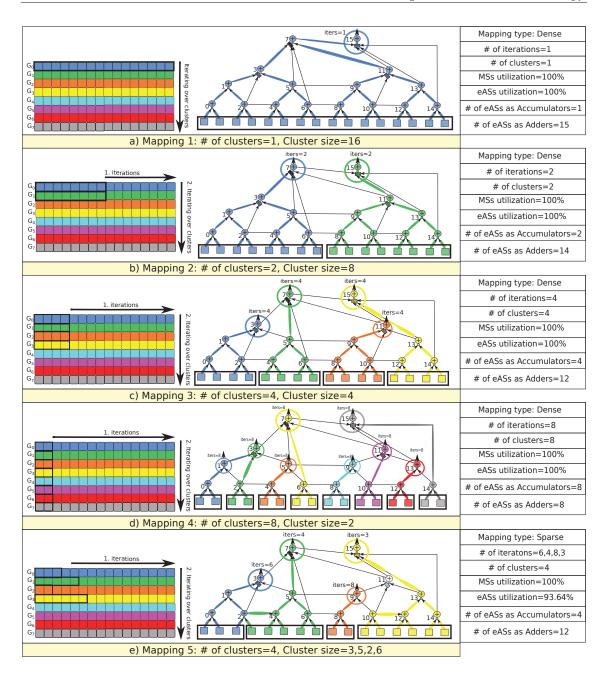

La segunda contribución de esta tesis se centra en la RN de aceleradores flexibles como MAERI o SIGMA. En concreto, estos diseños proponen como clave principal una RN específica (ART y FAN, respectivamente) para lograr la reducción flexible de distintos grupos de sumas parciales generadas por la MN. Estos grupos de sumas parciales pueden variar en tamaño debido al sparsity de la capa de DNN o incluso a sus características internas como su tamaño. En caso de que el grupo de sumas parciales pueda ser mapeado por completo en los multiplicadores, su acumulación es muy sencilla: basta con acumular todos los valores de forma espacial, utilizando los acumuladores del árbol de reducción. El problema que no es abordado en estas propuestas anteriores es lo que ocurre cuando el tamaño del grupo de sumas parciales supera al número de multiplicadores mapeados. En este caso, sumar todos los valores de forma espacial no es suficiente, y hay que recurrir a una suma espaciotemporal. Es decir, dividir el grupo de sumas parciales en distintas iteraciones, acumular espacialmente cada iteración y luego acumular de forma temporal (i.e., en distintos instantes de tiempo) el resultado de cada iteración. Este problema no es abordado de forma correcta en las propuestas de MAERI y SIGMA. Para resolverlo, una opción consiste en utilizar simplemente la RN nativa como ART y reenviar la suma parcial obtenida espacialmente en una iteración a través del Global Buffer hacia un multiplicador, para ser calculadas en la siguiente iteración. Este mecanismo denominado como S-Tree tiene dos inconvenientes principales: el primero es que impide mapeos óptimos, ya que al mapear un grupo de sumas parciales hay que dejar espacio para un multiplicador extra que es utilizado para reenviar la suma parcial de la iteración anterior que llega del Global Buffer. El segundo inconveniente y principal es que se genera una dependencia temporal entre dos iteraciones consecutivas, impidiendo que las iteraciones puedan ser ejecutadas de forma paralela en pipeline. Esto degrada significativamente el rendimiento. La segunda forma de resolver el problema evitando esta degradación de rendimiento es utilizar un esquema ST-Tree que

consiste en colocar un acumulador extra en cada nodo del árbol de reducción, permitiendo que la acumulación de distintas iteraciones pueda ser computada en paralelo junto con la acumulación espacial de las mismas. Esto se conoce como un *buffer* de acumulación y se utiliza en arquitecturas como la TPU de Google. El inconveniente de este esquema es que para lograr la flexibilidad que se propone en estas arquitecturas se necesita un acumulador en cada nodo del árbol de reducción, lo cual implica duplicar el número de unidades de suma, duplicando el área y el consumo energético del módulo de RN, el cual constituye hasta un 25 % y 38 % en área y energía, respectivamente, en aceleradores como MAERI y SIGMA. Esta sobrecarga es inasumible cuando el número de multiplicadores se incrementa en la arquitectura.

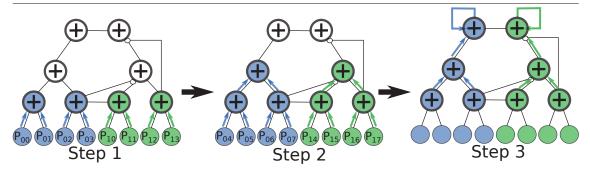

En esta tesis hemos diseñado una nueva propuesta de RN para solucionar este problema en arquitecturas flexibles. Nuestra propuesta se denomina STIFT (*Spatio-Temporal Integrated Folding Tree*) y consiste en utilizar un árbol de reducción similar a ART, pero añadiendo algunos enlaces extra entre los nodos, que aseguren que para cada nodo del árbol, siempre habrá un nodo conectado libre para realizar la acumulación. Esto permite aprovechar las unidades de suma ya existentes en el árbol y la única sobrecarga se debe a algunos enlaces extras y un nodo padre adicional en el árbol de reducción.

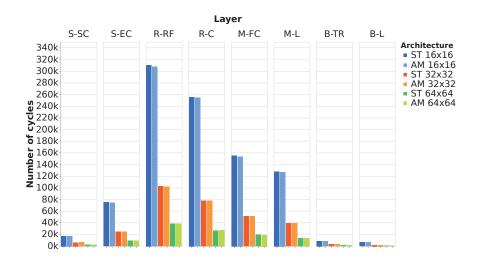

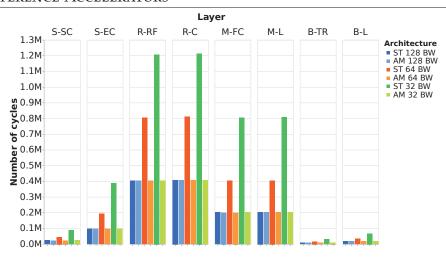

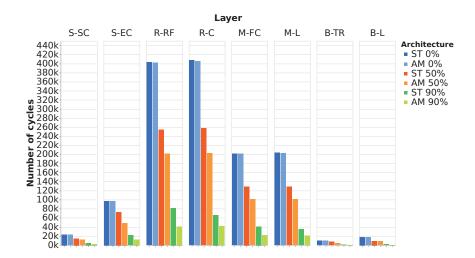

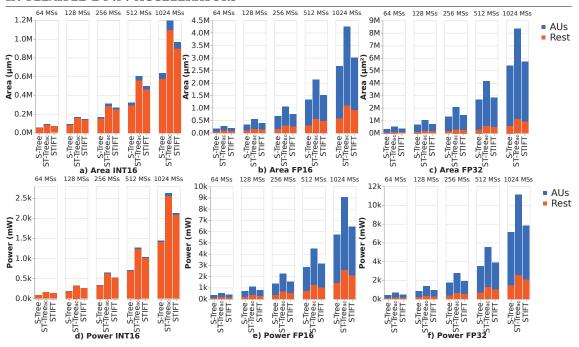

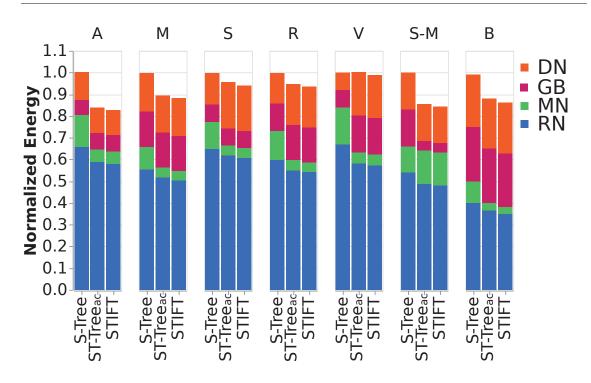

La evaluación de STIFT la hemos realizado desde tres ángulos diferentes: 1) una implementación RTL de S-Tree, ST-Tree y STIFT en Bluespec System Verilog [1] con el objetivo de comparar los resultados a nivel de área y energía. Para una evaluación exhaustiva hemos comparado los diseños para los tamaños de 64, 128, 256, 512 y 1024 multiplicadores. Además, comparamos los diseños para 3 tipos de datos distintos (INT16, FP16 y FP32).

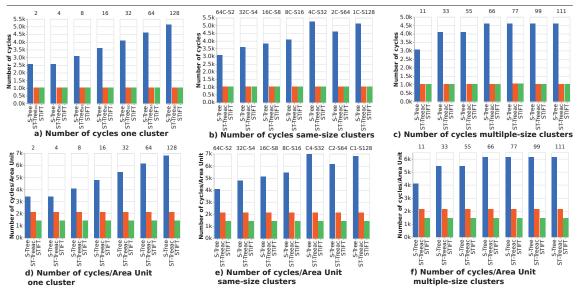

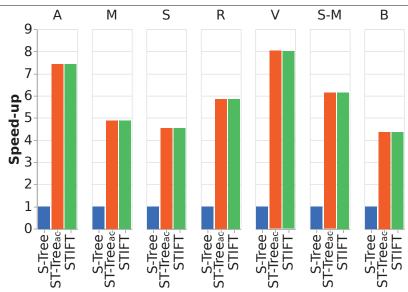

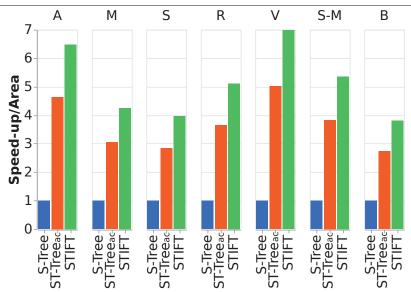

Para evaluar nuestra propuesta a nivel de rendimiento, hemos implementado S-Tree, ST-Tree y STIFT en nuestro simulador STONNE, utilizando como sistema base la RN ART y utilizando 256 multiplicadores 108-KiB de SRAM, 128 elementos/ciclo de ancho de banda de SRAM, y dos módulos de DRAM HBM 2.0, de 512 MiB cada uno y con un ancho de banda de 256 GB/s. Con esta configuración, hemos utilizado un estudio sintético consistente en mapear distintos tamaños de grupos de sumas parciales, así como la ejecución de 7 modelos de DNN reales completos extraídos de la suite de benchmarks MLPerf [107].

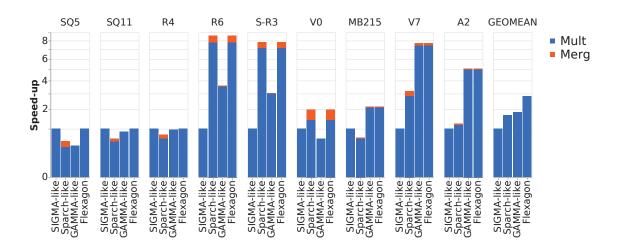

Los resultados obtenidos revelan que ST-Tree y STIFT obtienen el mismo rendimiento para todas las ejecuciones sintéticas y DNNs ya que ambas son capaces de ejecutar de forma paralela las disintas iteraciones de sumas parciales. Ambas, obtienen una mejora de rendimiento de hasta 8× para DNNs como VGG-16. Sin embargo, STIFT obtiene beneficios en términos de área y energía de

hasta 32 % y 31 %, con respecto ST-Tree ya que evita la duplicidad de las unidades de suma debido a su topología más inteligente. En otras palabras, STIFT logra una mejora de rendimiento/energía con respecto a S-Tree de  $5,13\times$ , mientras que ST-Tree solo logra un  $3,67\times$ .

Esta propuesta abordada en esta tesis supone un punto de inflexión en el diseño de aceleradores flexibles para DNNs ya que permite por primera vez ejecutar de forma eficiente grandes DNNs.

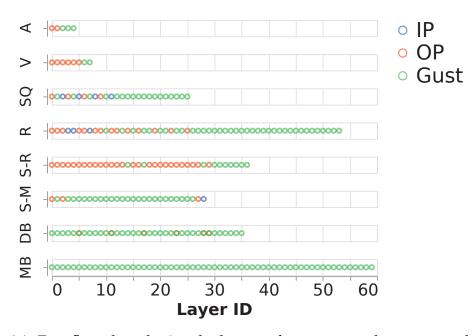

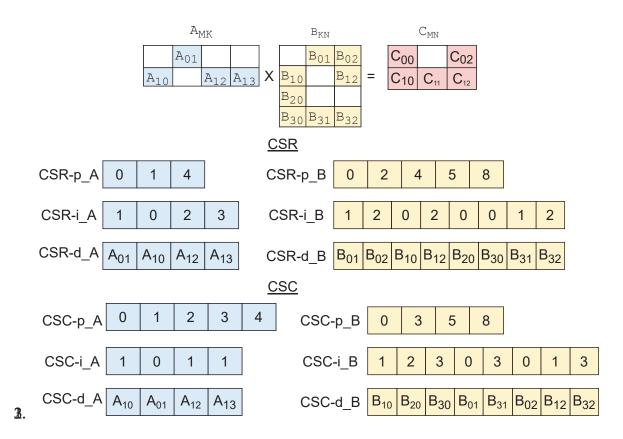

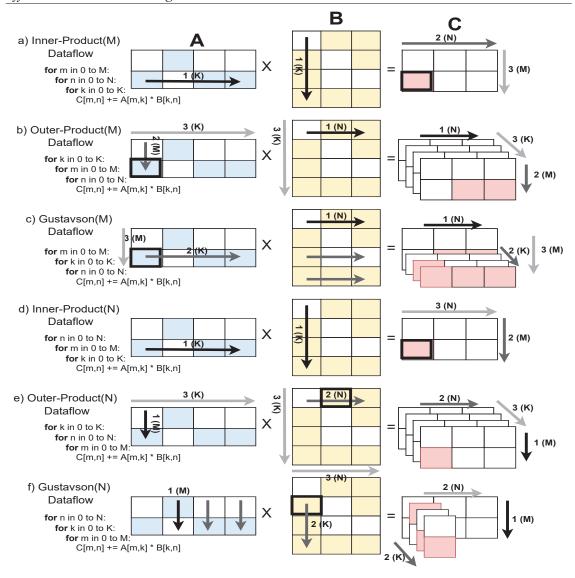

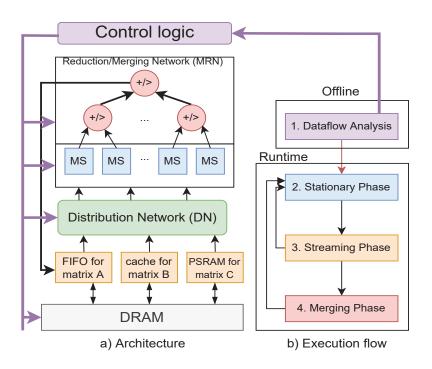

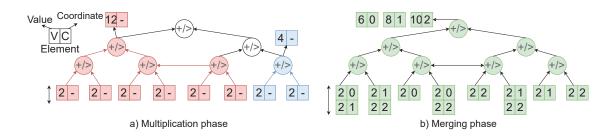

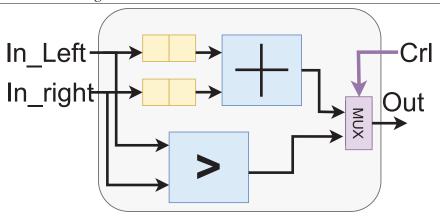

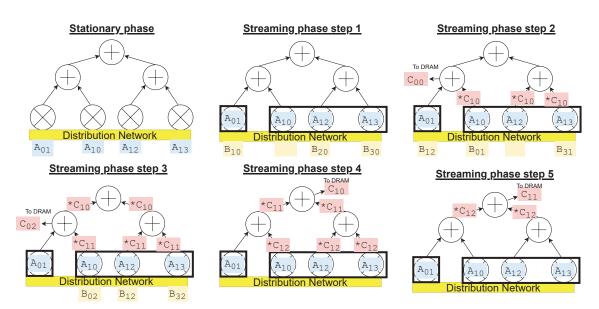

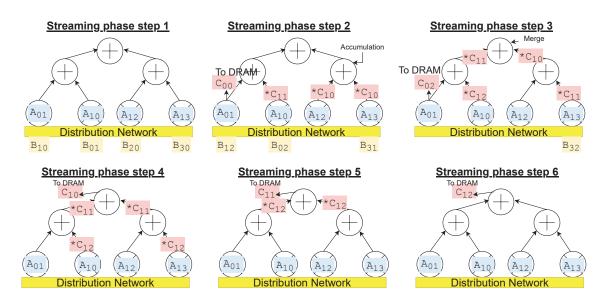

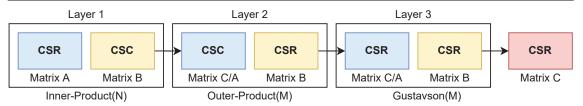

Estas propuestas anteriores como MAERI, SIGMA, nuestra propuesta STIFT o incluso otros aceleradores con soporte para ejecución de operaciones Sparse-Sparse Matrix Multiplication o SpMSpM (i.e., capas de DNNs cuyas matrices de activaciones y de pesos están comprimidas para eliminar los valores cero) [97, 98, 114, 122, 124], etc., tienen un inconveniente principal: están diseñados para ejecutar capas de DNNs utilizando un único dataflow. Por ejemplo, aceleradores como SIGMA [31] o ExTensor [50] ejecutan la operación SpMSpM utilizando un dataflow Inner Product (IP), requiriendo de ciertas unidades especiales para buscar los índices de ambas matrices que intersectan. Otros aceleradores como SpArch [124] o Outer-Space [97] están diseñados para ejecutar las capas SpMSpM utilizando un dataflow Outer Product (OP). De forma diferente, estos diseños requieren de estructuras tipo árbol para ejecutar una operación de ordenación (i.e., merge) entre distintos grupos de sumas parciales generados previamente. El inconveniente de este enfoque es que se generan una gran cantidad de sumas parciales que tienen que ser almacenadas en una memoria temporal. Finalmente, otros aceleradores como GAMMA [122] o MatRaptor [114] utilizan el dataflow Gustavson's (Gust), que de forma similar a OP generan sumas parciales y luego las ordenan, pero en este caso la generación y ordenación se hace fila a fila, reduciendo el número de sumas parciales temporales necesarias para ser almacenadas. Cada uno de estos enfoques tiene sus propias ventajas e inconvenientes y el rendimiento obtenido al ejecutar una determinada capa en un determinado dataflow depende especialmente del tamaño, y del patrón de sparsity que presente cada capa. Así, no existe un dataflow que se adapte bien para todos los tipos de capa y por tanto, todos los diseños mencionados anteriormente no son óptimos para ejecutar una DNN con cientos de capas. Para solucionar este problema, la tercera contribución de esta tesis es el diseño, presentación y evaluación de Flexagon, el primer acelerador específico para DNNs con soporte para la operación SpMSpM capaz de ejecutar los tres dataflows y por tanto capaz de adaptarse a cada capa a ejecutar. Flexagon está diseñado utilizando la estructura descrita anteriormente: una DN para distribuir los datos con soporte para los tres dataflows, una MN capaz de ejecutar operaciones de multiplicación y una nueva RN denominada

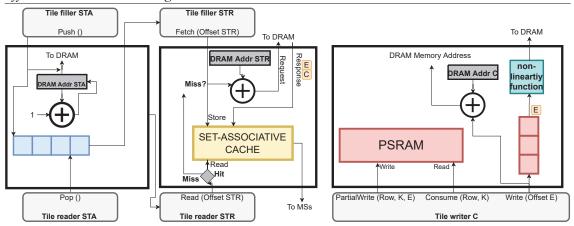

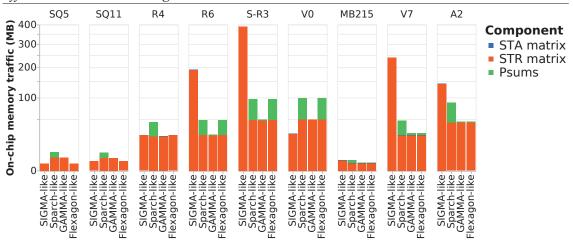

Merging-Reduction Network (MRN) que sirve para ejecutar ambas operaciones de acumulación y de ordenación, y por tanto, válida para adaptarse a los tres dataflows descritos anteriormente. Adicionalmente, Flexagon trae consigo un nuevo diseño de jerarquía de memoria que es capaz de adaptarse a los tres dataflows. Para ello, el primer nivel de la jerarquía se divide en 3 bloques de SRAM. Un primer bloque diseñado en forma de FIFO y que se utiliza para almacenar los datos que se mantienen más tiempo on-chip. Un segundo bloque de SRAM organizado como una caché tradicional pero utilizando tamaños de etiquetas reducidos y cuyo objetivo es capturar los patrones de acceso de memoria de los 3 dataflows, y un tercer bloque de memoria SRAM totalmente rediseñado en esta tesis denominado PSRAM. Esta estructura está especialmente diseñada para el almacenamiento temporal de las sumas parciales generadas en los dataflows OP y Gust, permitiendo un acceso eficiente en términos de energía, área y rendimiento. Junto con estos tres bloques de SRAM, hemos diseñado un único controlador de memoria unificado capaz de adaptarse y de generar las direcciones de memoria adecuadas para los 3 dataflows.

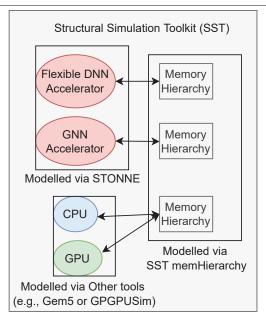

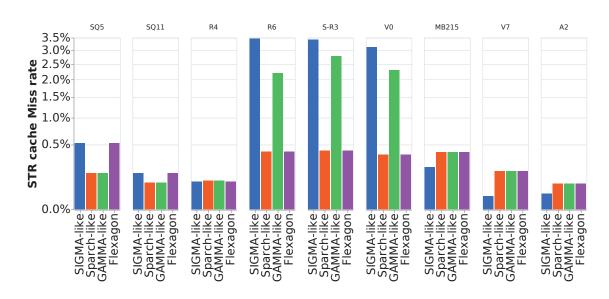

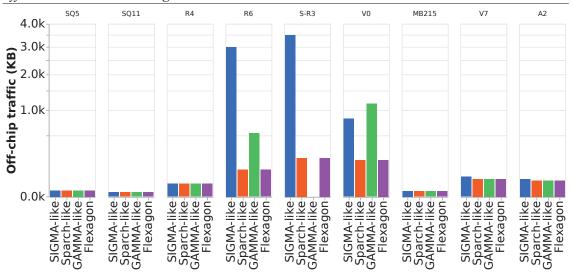

Para evaluar Flexagon hemos desarrollado un simulador a nivel de ciclo implementado en nuestro framework de simulación STONNE. En concreto, hemos utilizado una versión del simulador conectado al simulador SST [60] y que nos sirve para gestionar las peticiones de memoria que se generan de manera precisa. El simulador SST trae consigo un simulador de estructuras DRAM que nos permite conectar a nuestra jerarquía de memoria. Además, hemos implementado los aceleradores SIGMA (i.e., dataflow IP), SpArch (i.e., dataflow OP) y GAMMA (i.e., dataflow Gust) en el framework de simulación. Con el objetivo de comparar los resultados con Flexagon hemos configurado los 4 aceleradores con 64 multiplicadores, 16 elementos/ciclo de bandwidth, un tamaño para la estructura de memoria FIFO de 256 bytes, y un tamaño para la estructura caché de 1 MiB. Además, modelamos un tamaño de DRAM de 16 GiB y una latencia de 100 ns incorporando la tecnología HBM 2.0. Con estas cuatro configuraciones acelerador hemos realizado la ejecución de todas las capas para 8 modelos de DNNs extraídos de la suite de benchmarks MLPerf [107].

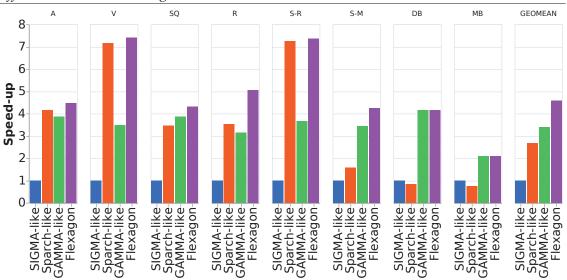

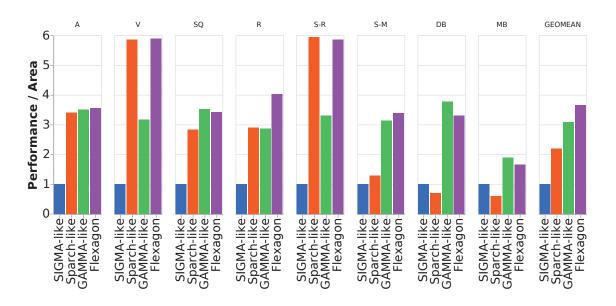

Los resultados obtenidos demuestran por primera vez que, tal y como predecíamos, no existe ningún *dataflow* que consiga el mejor rendimiento para todas las capas. Algunas DNNs como Alexnet, VGG-16, Resnets-50 y SSD-Resnets consiguen un  $5,26\times$  y  $1,49\times$  mejor rendimiento con una arquitectura tipo SpArch que con una arquitectura tipo SIGMA y GAMMA, respectivamente. Sin embargo, otras DNNs como Squeezenet, SSD-Mobilenets, DistilBert o MobileBert consiguen mejor rendimiento con GAMMA (mejora media de  $3,28\times$  y  $2,41\times$  con respecto

a SIGMA y SpArch, respectivamente). En consecuencia a este primer hecho, Flexagon supera a todas las propuestas anteriores, ya que es capaz de adaptarse en tiempo de ejecución a cada DNN y a cada capa de DNN. Cuantitativamente, los resultados obtenidos para Flexagon reflejan que nuestra propuesta obtiene beneficios de rendimiento medios de  $4,59\times$ ,  $1,71\times$  y  $1,35\times$  respecto a SIGMA, SpArch y GAMMA, respectivamente.

Además, en términos de área, Flexagon únicamente introduce un área adicional de 25 %, 3 % y 14 % con respecto a SIGMA, SpArch y GAMMA, respectivamente. De forma similar, el consumo con Flexagon incrementa un 25 % con respecto a SIGMA, un 9 % con respecto a SpArch y un 21 % con respecto a GAMMA. A pesar de este área y consumo extra introducidos, Flexagon todavía consigue beneficios en términos de rendimiento/área. Específicamente, los resultados revelan que Flexagon obtiene un 18 %, 67 % y 265 % mejor balance rendimiento/area con respecto a GAMMA, SpArch y SIGMA, respectivamente. Esto demuestra que Flexagon puede constituir un punto de inflexion en el futuro del diseño de los aceleradores específicos para DNNs con soporte para ejecución *sparse*.

# Índice

| Re  | esumen en castellano                                                                                                         | 14  |

|-----|------------------------------------------------------------------------------------------------------------------------------|-----|

| A٤  | gradecimientos                                                                                                               | 19  |

| Re  | esumen                                                                                                                       | 25  |

| Ín  | dice                                                                                                                         | 27  |

| Lis | sta de figuras                                                                                                               | 31  |

| Lis | sta de tablas                                                                                                                | 37  |

| 1   | Introducción                                                                                                                 | 39  |

| 2   | STONNE: Un simulador microarchitectural a nivel de ciclo para aceleradores de inferencia de DNNs                             | 61  |

| 3   | STIFT: Una red de interconexión on-chip para reducciones espacio-<br>temporales en aceleradores de DNNs flexibles            | 105 |

| 4   | Flexagon: Un acelerador multi-dataflow para multiplaciones de matrices sparse-sparse para un procesamiento eficiente de DNNs | 133 |

| 6   | Conclusiones y vías futuras                                                                                                  | 173 |

| Bi  | bliografía                                                                                                                   | 183 |

### **Agradecimientos**

El desarrollo de esta tesis doctoral ha sido sin lugar a dudas uno de los retos más complicados y a la vez de mayor aprendizaje de mi vida. Cuando comencé esta aventura académica hace cuatro años jamás habría imaginado la gran cantidad de personas que pasarían por mi vida, y lo mucho que tengo que agradecer a cada una de ellas.

En primer lugar, a ti Yolanda, mi pareja, mi amor. Realmente, es imposible para mí expresar en unas pocas palabras toda la gratitud y el amor que siento hacia ti. Gracias por formar equipo conmigo durante todo este tiempo. Gracias por acompañarme estos nueve años de carrera, máster y doctorado. Por sostenerme cuando tropezaba, levantarme cuando caía, e incluso tirar de mí cuando no podía levantarme. Gracias por escucharme de forma genuina, incluso cuando no entendías nada de lo que estaba diciendo. Gracias por apoyarme en cada curso, en cada clase, en cada examen, en cada trabajo y en cada paper. Eres un ejemplo de esfuerzo, apoyo, compromiso, fortaleza, humildad, honestidad, sinceridad y bondad. Has sido una inspiración para mí, y me siento muy afortunado de haber crecido como profesional y como persona a tu lado. Entre los miles de millones de personas que existen en el mundo, yo no he podido elegir a nadie mejor para ir de mi mano y espero que sepas que cada palabra de esta tesis doctoral también te pertenece, pues sin tu ayuda y apoyo jamás habría sido escrita.

También me gustaría agradecer enormemente a mis padres, por vuestro esfuerzo en cuidar siempre de mí, por la educación y valores que me habeis proporcionado y que tanto me han servido para superar cada uno de los obstáculos en el camino. Gracias por vuestras enseñanzas y lecciones, pues gracias a ellas he llegado al final de esta etapa y me siento capacitado para cualquier reto al que tenga que enfrentarme en la vida. En concreto, a ti mamá, por tu amor incondicional hacia mí durante todas las etapas de mi vida. Por tus charlas por la noche y por el día que tanto me enseñaban y me ayudaban a creer en mí y a ser

mejor persona. También a ti papá, por jugar conmigo de pequeño y por sentarte a mi lado a enseñarme matemáticas, ciencias, geografía y mucho más. Fuiste la llama que prendió mi curiosidad y que me inspiró hacia el desarrollo de esta tesis doctoral. A mis abuelos Santos y Kiki, y a mis abuelas Gregoria y Bernarda. Gracias a los que estáis y a los que ya no. Por vuestro amor incondicional, aprendizajes y apoyo durante las distintas etapas de mi vida. Os llevo y llevaré siempre en mi corazón. A todos mis tíos y tías Juanje, Glori, Conchi y Ángel. Gracias por haberme hecho sentir siempre tan querido, por apoyarme en mis decisiones, por creer siempre en mí, y por motivarme hacia esta meta, como hacía tantas otras. A mis dos únicos primos Juan Jesús y Alejandra que para mí siempre han sido y serán como hermanos. A ti Juan Jesús, por acompañarme durante toda mi infancia y cuyo ejemplo siempre me ha inspirado para ser mejor persona. A ti Alejandra, porque a pesar de nuestra diferencia de edad, siempre he podido sentir tu cariño y apoyo incondicional. A mis suegros Paqui y Eduardo, junto con mi cuñado Dani, además de al resto de mi familia política, Antonia y José. Gracias a todos vosotros por cuidar siempre de mí. Por incluirme desde el primer día en vuestra familia como uno más y por tratarme como tal. Gracias por creer en mí todos estos años, por celebrar mis alegrías cómo vuestras y por hacerme sentir que podía lograrlo. Sois también una parte fundamental en mi vida, y me siento muy orgulloso de ello.

A Díaz y Carmen. A ti Díaz, por creer en mí, por permanecer siempre a mi lado desde los tres años de edad y demostrarme que la verdadera amistad es inmutable al tiempo y al espacio. Por ser un ejemplo de fortaleza frente a la vida. También a ti Carmen, por nuestras conversaciones en el autobús durante mis primeros años en la universidad, por empujarme a confiar en mí mismo, y por ayudarme siempre en todo lo que he necesitado durante estos años.

A todos mis "thunderfriends": Luis, Alberto, Javi, Juan Antonio, Puri, Manu, Laura, Lucía, Juan Antonio, Noemi, Morad, y Dani. Gracias por todas las conversaciones que solo nosotros entendemos. Gracias por todos los momentos y fiestas inolvidables que tanto me hacían disfrutar y desconectar. Y gracias por apoyarme durante todo este camino. Aunque últimamente ya no nos podemos ver muy frecuentemente, os llevo siempre conmigo.

A mis directores de tesis, Manolo y José Luis. Gracias a ambos por confiar en mí para la realización de este proyecto. Nunca es fácil comenzar algo desde cero, y sin embargo, vosotros no dudasteis de mí ni un instante. Habéis sido la luz que ha guiado mi camino. Incluso en los momentos más oscuros, habéis sabido encender la llama de la motivación y me habéis sacado de allí de la mano, trabajando siempre a mi lado, de forma muchas veces totalmente altruista.

Además, gracias a ti Manolo, por descubrirme en tercero de carrera. Porque yo no lo sabía, pero aquella primera reunión en tu despacho cambiaría mi trayectoria profesional para siempre. Gracias por abrirme al mundo de la investigación y hacerme conocer las oportunidades que puede ofrecer. También gracias a ti José Luis, por contagiarme tu motivación por la docencia y la investigación. Por hacerme sentir que podía lograrlo, y por todo el esfuerzo, humildad y honestidad que has puesto en cada uno de nuestros trabajos y que siempre ayudaban a mejorarlos.

Special thanks to Professor Tushar Krishna. Thank you for being my third (although not official) thesis director. One day you looked up your mailbox and came across an email from three random researchers that had just started a new project. Other person could have simply ignored the email. However, rather than that, you set up a meeting and started a close collaboration with us. You included us within your group and even welcomed me with open arms in your Synergy lab. You allowed me to live in the USA, which was one of the most enrichment experiences of my whole life. You honor the name of your group by being an example of modesty, inclusion, and synergy. Thank you for everything, Tushar. Moreover, to Michael Pellauer. Thank you for joining us this last year and for adding your enormous experience in this research field. You are one of the best researchers I have ever worked with, and without you, the development of Flexagon, the last contribution of this thesis, would have never been come alive. To all my colleagues at the University of Murcia: Eduardo, David, Ashkan, Sawan, Víctor, Sebastian, Pablo, Alejandro, Vahid and Ayyoub. You are the best I take away from this thesis. Thank you for all our lunches, dinners, and parties. For the endless technical discussions. For listening to me when I needed someone and, in essence, thanks for all your support during this time. To me, you are not just colleagues, you are family, and you will ever be. To all my colleagues at the Georgia Institute of Technology: Eric, Saeed, Abhimanyu, Canlin, Jinsun, Jianming, Geonhwa, and Anand. Thanks for your support and endless help during my life in Atlanta. Special thanks here to Raveesh, for your help and efforts during this thesis, our endless and helpful technical discussions, and for your genuine support during the hardest moments of my stay at Georgia Tech.

También, me gustaría mencionar a aquellas personas que pasaron por mi vida durante el grado y el máster, pues me ayudasteis a superar cada uno de los duros desafíos: Marcelo, Alejandro, Adrián, Victoriano, Puri, Laura, José María, Jesús, Serena, Guillermo y muchos más. Aquí, me gustaría mencionar especialmente a mi compañero de prácticas, José María (a.k.a., Queque). Gracias por la motivación que me diste durante los primeros años. Sin ti, siento que jamás me habría enamorado tanto de la informática y probablemente hoy no

estaría aquí escribiendo estás líneas. Te estaré siempre agradecido por todo tu apoyo.

A mi terapeuta Diego, por acompañarme durante este último año. Gracias por ayudarme a conocerme un poco más y empujarme a realizar los cambios que necesitaba en este momento de mi vida. Eres un gran ejemplo de profesional y me siento afortunado de haberte encontrado.

Finalmente, agradecer también a la Fundación Séneca (Agencia de Ciencia y Tecnología de la Región de Murcia) por su apoyo económico mediante una Beca-Contrato Predoctoral de Formación del Personal Investigador (FPI).

A cada uno de vosotros, muchísimas gracias por hacer todo esto posible. *To all of you, thank you very much for making all this possible.*

### Universidad de Murcia Facultad de Informática

Departamento de Ingeniería y Tecnología de Computadores

## Hardware Techniques for the Design of Efficient Inference Accelerators of Deep Neural Networks

PhD Thesis

By Francisco Muñoz Martínez

Advised by Manuel Eugenio Acacio Sánchez José Luis Abellán Miguel

Murcia, Septiembre 2022

#### **Abstract**

The design of specialized architectures for accelerating the inference procedure of Deep Neural Networks (DNNs) is a booming area of research nowadays. While first-generation rigid accelerator proposals used simple fixed dataflows tailored for dense DNNs, more recent architectures have argued for flexibility to efficiently support a wide variety of layer types, dimensions, and sparsity. As the complexity of these accelerators grows, the analytical models currently being used for design-space exploration are unable to capture execution-time subtleties, leading to inexact results in many cases as we demonstrate. This opens up a need for cycle-level simulation tools to allow for fast and accurate design-space exploration of DNN accelerators, and rapid quantification of the efficacy of architectural enhancements during the early stages of a design. To this end, the first contribution of this thesis is STONNE (*Simulation TOol of Neural* Network Engines), a cycle-level microarchitectural simulation framework that can plug into any high-level DNN framework as an accelerator device and perform full-model evaluation (i.e. we are able to simulate real, complete, unmodified DNN models) of state-of-the-art rigid and flexible DNN accelerators, both with and without sparsity support. As a proof of concept, we use STONNE in three use cases: i) a direct comparison of three dominant inference accelerators using real DNN models; ii) back-end extensions and iii) front-end extensions of the simulator to showcase the capability of STONNE to rapidly and precisely evaluate data-dependent optimizations. Once, we have a validated simulator to perform our evaluations, the second contribution of this thesis focuses the attention on the flexible architectures for DNNs. DNN accelerators use three separate NoCs within the accelerator, namely distribution, multiplier and reduction networks (or DN, MN and RN, respectively) between the global buffer(s) and compute units (multipliers/adders). These NoCs enable data delivery, and more importantly, onchip reuse of operands and outputs to minimize the expensive off-chip memory

accesses. Among them, the RN, used to generate and reduce the partial sums produced during DNN processing, is what implies the largest fraction of chip area (25% of the total chip area in some cases) and power dissipation (38% of the total chip power budget), thus representing a first-order driver of the energy efficiency of the accelerator.

RNs can be orchestrated to exploit a Temporal, Spatial or Spatio-Temporal reduction dataflow. Among these, the latter is the one that has shown superior performance. However, as we demonstrate, a state-of-the-art implementation of the Spatio-Temporal reduction dataflow, based on the addition of Accumulators (Ac) to the RN (i.e. RN+Ac strategy), can result into significant area and energy expenses. To cope with this important issue, we propose STIFT (that stands for *Spatio-Temporal Integrated Folding Tree*) that implements the Spatio-Temporal reduction dataflow entirely on the RN hardware substrate (i.e. without the need of the extra accumulators). STIFT results into significant area and power savings regarding the more complex RN+Ac strategy, at the same time its performance advantage is preserved.

The third contribution of this thesis increases the flexibility current sparse accelerators by adding support for more dataflows.

Existing Sparse-Sparse Matrix Multiplication (SpMSpM) accelerators are tailored to a particular SpMSpM dataflow (i.e., Inner Product, Outer Product or Gustavson's), that determines their overall efficiency. We demonstrate that this static decision inherently results in a suboptimal dynamic solution. This is because different SpMSpM kernels show varying features (i.e., dimensions, sparsity pattern, sparsity degree), which makes each dataflow better suited to different data sets.

Motivated by this observation, we propose Flexagon, the first SpMSpM reconfigurable accelerator that is capable of performing SpMSpM computation by using the particular dataflow that best matches each case. Flexagon accelerator is based on a novel Merger-Reduction Network (MRN) that unifies the concept of reducing and merging in the same substrate, increasing efficiency. Additionally, Flexagon also includes a 3-tier memory hierarchy, specifically tailored to the different access characteristics of the input and output compressed matrices. Using detailed cycle-level simulation of contemporary DNN models from a variety of application domains, we show that Flexagon achieves average performance benefits of  $4.59\times$ ,  $1.71\times$ , and  $1.35\times$  with respect to the state-of-the-art SIGMA-like, SpArch-like and GAMMA-like accelerators (265% , 67% and 18%, respectively, in terms of average performance/area efficiency).

### **Contents**

| Ex | tend  | ed abstract in Spanish                       | 5  |

|----|-------|----------------------------------------------|----|

| Ta | ble o | of contents in Spanish                       | 15 |

| A  | cknov | wledgments                                   | 19 |

| Al | bstra | ct                                           | 25 |

| Co | onten | .ts                                          | 27 |

| Li | st of | Figures                                      | 31 |

| Li | st of | Tables                                       | 37 |

| 1  | Intr  | oduction                                     | 39 |

|    | 1.1   | Towards General-Purpose Processors           | 40 |

|    | 1.2   | Towards Specialized Compute Processors       | 41 |

|    | 1.3   | Machine Learning                             | 44 |

|    |       | 1.3.1 Deep Learning                          | 45 |

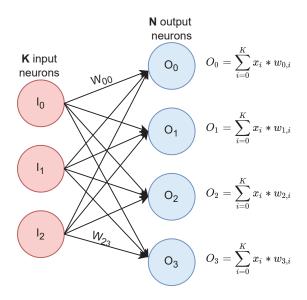

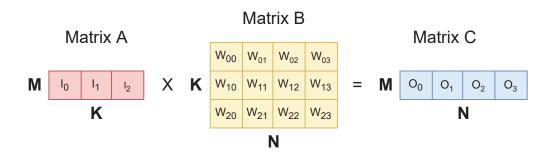

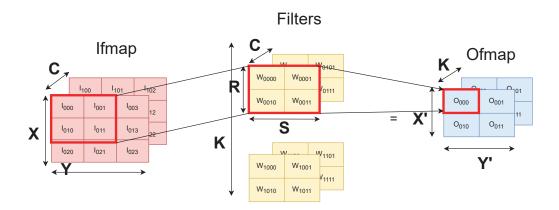

|    |       | 1.3.2 Deep Neural Networks                   | 47 |

|    | 1.4   | Specific Architectures for DNNs              | 53 |

|    |       | 1.4.1 Rigid DNN Accelerator Architectures    | 54 |

|    |       | 1.4.2 Flexible DNN Accelerator Architectures | 54 |

|    |       | 1                                            | 55 |

|    | 1.5   | Thesis Motivations and Contributions         | 56 |

|    |       | 1.5.1 Publications Derived from this Thesis  | 58 |

|    | 16    | Thesis Organization                          | 59 |

#### Contents

| 2 |       |         | Enabling Cycle-Level Microarchitectural Simulation for      |    |

|---|-------|---------|-------------------------------------------------------------|----|

|   |       |         |                                                             | 61 |

|   | 2.1   |         |                                                             | 61 |

|   | 2.2   |         |                                                             | 65 |

|   |       | 2.2.1   | 3                                                           | 66 |

|   |       | 2.2.2   | $\mathcal{I}$                                               | 69 |

|   | 2.3   |         |                                                             | 70 |

|   |       | 2.3.1   |                                                             | 71 |

|   |       | 2.3.2   | T                                                           | 72 |

|   |       | 2.3.3   | 1                                                           | 73 |

|   |       | 2.3.4   |                                                             | 73 |

|   | 2.4   |         | O                                                           | 75 |

|   |       | 2.4.1   | 1                                                           | 75 |

|   |       | 2.4.2   |                                                             | 80 |

|   |       | 2.4.3   | O                                                           | 81 |

|   | 2.5   |         |                                                             | 83 |

|   |       | 2.5.1   | O                                                           | 83 |

|   |       | 2.5.2   |                                                             | 85 |

|   |       | 2.5.3   | 7 67                                                        | 85 |

|   | 2.6   | -       | L                                                           | 85 |

|   |       | 2.6.1   | ,                                                           | 85 |

|   |       | 2.6.2   | 1 1                                                         | 88 |

|   |       | 2.6.3   | Front-End Extension for Filter Scheduling in Sparse Accel-  |    |

|   |       |         |                                                             | 92 |

|   | 2.7   |         | nal Tools based on STONNE                                   |    |

|   |       | 2.7.1   |                                                             | 00 |

|   |       | 2.7.2   | SST-STONNE                                                  |    |

|   | 2.8   | Concl   | usions                                                      | 02 |

| 3 | STI   | FT: A n | ovel network fabric for efficient spatio-temporal reduction |    |

|   | in fl | exible  | DNN accelerators 1                                          | 05 |

|   | 3.1   |         |                                                             | 05 |

|   | 3.2   | Backg   | round and Related Work                                      | 09 |

|   |       | 3.2.1   | Reduction Networks in Rigid Accelerators                    |    |

|   |       | 3.2.2   | Reduction Networks in Flexible Accelerators                 |    |

|   | 3.3   | STIFT   | : A Spatio-Temporal Integrated Folding Tree                 | 14 |

|   |       | 3.3.1   | STIFT Topology                                              |    |

|   |       | 337     | Microarchitectural Implications of STIFT 1                  | 17 |

|      | 3.3.3                                       | STIFT Mappings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.4  | Exper                                       | imental Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 3.4.1                                       | RTL Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 3.4.2                                       | Synthetic Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 3.4.3                                       | End-to-End Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.5  | Resul                                       | ts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 3.5.1                                       | RTL Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 3.5.2                                       | Synthetic Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 3.5.3                                       | End-to-End Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

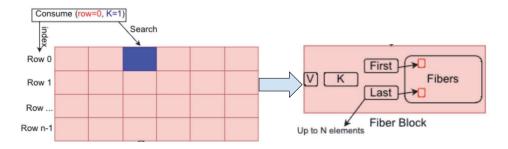

| 3.6  | Concl                                       | usions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |