UNIVERSIDAD DE MURCIA Departamento de Ingeniería y Tecnología de Computadores

# Fault-tolerant Cache Coherence Protocols for CMPs

A dissertation submitted in fulfillment of the requirements for the degree of

Doctor en Informática

By Ricardo Fernández Pascual

Advised by José Manuel García Carrasco Manuel Eugenio Acacio Sánchez

Murcia, June 2009

UNIVERSIDAD DE MURCIA Departamento de Ingeniería y Tecnología de Computadores

# Protocolos de Coherencia Tolerantes a Fallos

Tesis propuesta para la obtención del grado de

Doctor en Informática

Presentada por Ricardo Fernández Pascual

Supervisada por José Manuel García Carrasco Manuel Eugenio Acacio Sánchez

Murcia, Junio de 2009

UNIVERSIDAD DE MURCIA DEPARTAMENTO DE INGENIERÍA Y TECNOLOGÍA DE COMPUTADORES

D. José Manuel García Carrasco, Catedrático de Universidad del Área de Arquitectura y Tecnología de Computadores en el Departamento de Ingeniería y Tecnología de Computadores

y

D. Manuel Eugenio Acacio Sánchez, Profesor Titular de Universidad del Área de Arquitectura y Tecnología de Computadores en el Departamento de Ingeniería y Tecnología de Computadores

AUTORIZAN:

La presentación de la Tesis Doctoral titulada «*Fault-tolerant Cache Coherence Protocols for CMPs*», realizada por D. Ricardo Fernández Pascual, bajo su inmediata dirección y supervisión, y que presenta para la obtención del grado de Doctor por la Universidad de Murcia.

En Murcia, a de Junio de 2009.

Fdo: Dr. José Manuel García Carrasco

Fdo: Dr. Manuel Eugenio Acacio Sánchez

D. Antonio Javier Cuenca Muñoz, Profesor Titular de Universidad del Área de Arquitectura y Tecnología de Computadores y Director del Departamento de Ingeniería y Tecnología de Computadores, INFORMA:

Que la Tesis Doctoral titulada *«Fault-tolerant Cache Coherence Protocols for CMPs»*, ha sido realizada por D. Ricardo Fernández Pascual, bajo la inmediata dirección y supervisión de D. José Manuel García Carrasco y de D. Manuel Eugenio Acacio Sánchez, y que el Departamento ha dado su conformidad para que sea presentada ante la Comisión de Doctorado.

En Murcia, a de Junio de 2009.

Fdo: Dr. Antonio Javier Cuenca Muñoz

A María Dolores y José Ricardo

## Abstract

Technology trends are making possible to put billions of transistors in a single chip, which has allowed computer architects to build single-chip multiprocessors (CMPs). Unfortunately, these trends of miniaturization also mean that the reliability of individual transistors decreases. This way, transient faults, which were once a serious problem only for memories and in extreme environments like aerospatial applications, are expected to be a problem for future many-core CMPs. One of the components prone to experience transient faults in CMP systems will be the on-chip interconnection network.

In this thesis, we propose a new way to deal with transient faults in the interconnection network that is different from the classic approach of building a fault-tolerant interconnection network. In particular, we propose to provide fault tolerance measures at the level of the cache coherence protocol so that it guarantees the correct execution of parallel programs even when the underlying interconnection network does not necessarily deliver all messages correctly. By doing this, we can take advantage of the different meaning of each message to implement fault tolerance with lower overhead than at the level of the interconnection network, which has to treat all messages alike with respect to reliability.

To demonstrate the viability of our approach, we design a number of faulttolerant cache coherence protocols. First, we design FTTOKENCMP, based on the token coherence framework. FTTOKENCMP adds timeouts for fault detection and simple recovery mechanisms for transient faults to a previously proposed tokenbased cache coherence protocol. We also extend the general token counting rules to ensure reliable transference of owned data, to simplify the application of these fault tolerance measures to other cache coherence protocols based on the token framework. Secondly, we design FTDIRCMP: a directory-based fault-tolerant cache coherence protocol which adds measures inspired by the previous work

#### Abstract

in FTTOKENCMP. Finally, the same ideas are used to design FTHAMMERCMP: a broadcast-based and snoopy-like fault-tolerant cache coherence protocol based on the cache coherence protocol used by AMD in their Opteron processors.

We evaluate the proposed protocols using full-system simulation of several parallel applications. The results of this evaluation show that, in absence of faults, our fault tolerance measures do not increase significantly the execution time of the applications and that their major cost is an increase in network traffic due to acknowledgment messages that ensure the reliable transference of ownership between coherence nodes, which are sent out of the critical path of cache misses. The results also show that a system using our protocols degrades gracefully when transient faults in the interconnection network actually happen, supporting faults rates which are much higher than expected in the real world with only a small increase in the execution time.

## Acknowledgments

Completing this thesis has by no means been an easy task for me. However, the experience has been very good on the whole thanks to the help of many people that deserve credit for the final result. At least for the good parts.

First, I would like to thank my advisors, Prof. José Manuel García Carrasco and Dr. Manuel Acacio Sánchez for having me as a PhD student during almost five years. They have taught me how to perform research in computer architecture and they have always shown encouraging support for me and my work, helping me well beyond their professional duties. Prof. José Duato, coauthor of all my papers related with this thesis, has also provided very important technical advice, and he was the one who suggested this line of research in the first place.

I would like to thank Dr. Mikel Luján and Prof. Frank Wang for reviewing this thesis and providing useful comments.

I have had the luck to perform this work at the *Departamento de Ingeniería y Tecnología de Computadores* of the *Universidad de Murcia*. All the members of the department have always been ready to help me whenever I asked, and sometimes even before I asked. I am specially thankful for their help during my first years teaching computer architecture.

This thesis and my formation as a researcher have benefited greatly from the influence of the rest of the PhD students of my research group (GACOP). Amongst them, I should mention first Alberto Ros Bardisa, who has helped me in everything that I have done related to computer architecture since before I suspected that I would be one day writing a thesis in this area. I have also enjoyed many discussions (not only about computer architecture) with most of the students, specially those who joined the research group during my first years of PhD studies: Juan Manuel Cebrían González, José María Cecilia Canales, Daniel Sánchez Pedreño and Ruben Titos Gil. I also want to thank them for their work on keeping our computing cluster up and running.

#### Acknowledgments

My friends have helped me to avoid losing my sanity by keeping me away from my work from time to time. I have tried to make a list of those who I should mention by name, but I cannot come up with a list short enough to put it here. They know who they are, anyway.

In the end, this thesis has only been possible because my family has supported me during all these years. My parents, aunts and uncles deserve the largest share of the merits.

# Contents

| Ał | ostrac | et                                                   | 11 |

|----|--------|------------------------------------------------------|----|

| Ac | knov   | vledgments                                           | 13 |

| Co | onten  | ts                                                   | 15 |

| Ta | ble o  | f contents in Spanish                                | 19 |

| Li | st of  | Figures                                              | 21 |

| Li | st of  | Tables                                               | 25 |

| Li | st of  | Acronyms                                             | 27 |

| Ex | tend   | ed abstract in Spanish                               | 29 |

| 1  | Intr   | oduction                                             | 49 |

|    | 1.1    | Tiled Chip Multiprocessors                           | 50 |

|    | 1.2    | Cache coherence and interconnection networks         | 51 |

|    | 1.3    | Reliability of future electronic devices             | 54 |

|    | 1.4    | Motivation                                           | 55 |

|    | 1.5    | Contributions                                        | 57 |

|    | 1.6    | Organization of this thesis                          | 59 |

| 2  | Rela   | ated work                                            | 61 |

|    | 2.1    | Fault-tolerant multiprocessors                       | 61 |

|    | 2.2    | Fault tolerance in CMPs                              | 64 |

|    | 2.3    | Fault tolerance at the interconnection network level | 66 |

#### Contents

| 3 | General assumptions and fault tolerance requirements for cache co- |                                                                    |     |  |  |

|---|--------------------------------------------------------------------|--------------------------------------------------------------------|-----|--|--|

|   |                                                                    | ence protocols                                                     | 69  |  |  |

|   | 3.1                                                                | J 1                                                                | 69  |  |  |

|   | 3.2                                                                | Requirements for a fault-tolerant cache coherence protocol         | 72  |  |  |

| 4 | A to                                                               | oken-based fault-tolerant cache coherence protocol                 | 75  |  |  |

|   | 4.1                                                                | Problems caused by an unreliable interconnection network in To-    |     |  |  |

|   |                                                                    | KENCMP                                                             | 76  |  |  |

|   | 4.2                                                                | Fault tolerance measures introduced by FTTOKENCMP                  | 78  |  |  |

|   |                                                                    | Token counting rules for reliable data transference                | 79  |  |  |

|   |                                                                    | Fault detection                                                    | 81  |  |  |

|   |                                                                    | Avoiding data loss                                                 | 81  |  |  |

|   |                                                                    | Dealing with token loss                                            | 88  |  |  |

|   |                                                                    | Dealing with faults in persistent requests                         | 89  |  |  |

|   |                                                                    | Token recreation process                                           | 92  |  |  |

|   | 4.3                                                                | Hardware overhead of FtTokenCMP                                    | 97  |  |  |

| 5 | A d                                                                | irectory-based fault-tolerant cache coherence protocol             | 101 |  |  |

|   | 5.1                                                                | Problems caused by an unreliable interconnection network in        |     |  |  |

|   |                                                                    | DIRCMP                                                             | 102 |  |  |

|   | 5.2                                                                | Fault tolerance measures introduced by FTDIRCMP                    | 104 |  |  |

|   |                                                                    | Reliable data transmission                                         |     |  |  |

|   |                                                                    | Faults detected by the <i>lost request timeout</i>                 | 113 |  |  |

|   |                                                                    | Faults detected by the <i>lost unblock timeout</i>                 |     |  |  |

|   |                                                                    | Faults detected by the lost backup deletion acknowledgment timeout |     |  |  |

|   |                                                                    | Faults detected with the <i>lost data timeout</i>                  |     |  |  |

|   |                                                                    | Reissuing requests and request serial numbers                      |     |  |  |

|   |                                                                    | Ping messages                                                      |     |  |  |

|   |                                                                    | Taking advantage of a point-to-point ordered network               |     |  |  |

|   | 5.3                                                                | Hardware overhead of FTDIRCMP                                      |     |  |  |

| 6 | A b                                                                | roadcast-based fault-tolerant cache coherence protocol             | 131 |  |  |

|   | 6.1                                                                | A cache coherence protocol for CMPs based on AMD's Hammer          |     |  |  |

|   |                                                                    |                                                                    | 132 |  |  |

|   |                                                                    | Problems caused by an unreliable interconnection network in HAM-   |     |  |  |

|   |                                                                    | MERCMP                                                             | 133 |  |  |

|   | 6.2                                                                | Fault tolerance measures introduced by FTHAMMERCMP                 |     |  |  |

|   |                                                                    | 5                                                                  |     |  |  |

|      | Summary of differences of the fault tolerance measures of FTHAM-                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | MERCMP and FTDIRCMP                                                                                                                                                                                                | 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Eva  | uation methodology                                                                                                                                                                                                 | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7.1  |                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.2  |                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.3  | •                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | * *                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | **                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | -                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | Other scientific applications                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Eva  | luation results                                                                                                                                                                                                    | 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8.1  | Overhead without faults                                                                                                                                                                                            | 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | Execution time overhead                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | Network traffic overhead                                                                                                                                                                                           | 153                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8.2  | Performance degradation under faults                                                                                                                                                                               | 157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | Execution slowdown                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | Network traffic increase                                                                                                                                                                                           | 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | Effect of bursts of faults                                                                                                                                                                                         | 163                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8.3  | Adjusting fault tolerance parameters                                                                                                                                                                               | 165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | Adjusting the backup buffer size in FTTOKENCMP                                                                                                                                                                     | 165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | Adjusting the fault detection timeouts                                                                                                                                                                             | 167                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

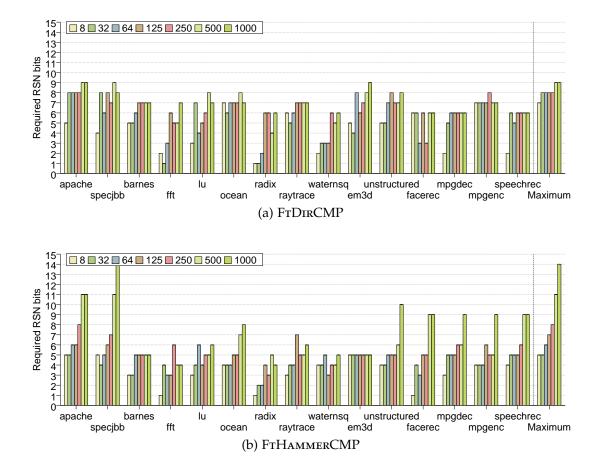

|      | Adjusting request serial number sizes for FTDIRCMP and FTHAM-                                                                                                                                                      | 170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 84   |                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0.1  |                                                                                                                                                                                                                    | 175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Con  | clusions and future ways                                                                                                                                                                                           | 177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9.1  | Conclusions                                                                                                                                                                                                        | 177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9.2  | Future ways                                                                                                                                                                                                        | 180                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Base | e token-based protocol                                                                                                                                                                                             | 183                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Base | e directory-based protocol                                                                                                                                                                                         | 187                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Mes  | sage dependency chains of our directory-based protocols                                                                                                                                                            | 191                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | <ul> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li><b>Eval</b></li> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li><b>Con</b></li> <li>9.1</li> <li>9.2</li> <li><b>Base</b></li> <li><b>Base</b></li> </ul> | MERCMP and FTDIRCMP         Evaluation methodology         7.1         Failure model         7.2         Configuration of the simulated systems         7.3         Applications         Server applications         Apache         SpecJbb         Applications from SPLASH-2         Applications from ALTPBench         Other scientific applications         Other scientific overhead         Network traffic overhead         Network traffic overhead         Network traffic increase         Effect of bursts of faults         8.3       Adjusting fault tolerance parameters         Adjusting the fault detection timeouts         Adjusting the fault detection timeouts         Adjusting request serial number sizes for FTDIRCMP and FTHAM-MERCMP         8.4         Hardware implementation overheads         Sourclusions and future ways         9.1         Conclusions |

### Bibliography

195

# Índice

| Ín                 | dice                                                                                          | 19  |

|--------------------|-----------------------------------------------------------------------------------------------|-----|

| Lista de figuras 2 |                                                                                               |     |

| Li                 | sta de tablas                                                                                 | 25  |

| Li                 | sta de acrónimos                                                                              | 27  |

| Re                 | esumen en español                                                                             | 29  |

| 1                  | Introducción                                                                                  | 49  |

| 2                  | Trabajo relacionado                                                                           | 61  |

| 3                  | Suposiciones generales y requerimientos para los protocolos de coherencia tolerantes a fallos | 69  |

| 4                  | Diseño de un protocolo de coherencia basado en tokens tolerante a<br>fallos                   | 75  |

| 5                  | Diseño de un protocolo de coherencia basado en directorio tolerante<br>a fallos               | 101 |

| 6                  | Diseño de un protocolo de coherencia basado en broadcast tolerante<br>a fallos                | 131 |

| 7                  | Metodología de evaluación                                                                     | 137 |

| 8                  | Resultados de evaluación                                                                      | 149 |

### Índice

| 9  | Conclusiones y vías futuras                                                             | 177 |

|----|-----------------------------------------------------------------------------------------|-----|

| A  | Protocolo base basado en tokens                                                         | 183 |

| B  | Protocolo base basado en directorio                                                     | 187 |

| C  | Cadenas de dependencias de mensajes para nuestros protocolos ba-<br>sados en directorio | 191 |

| Bi | bliografía                                                                              | 195 |

# **List of Figures**

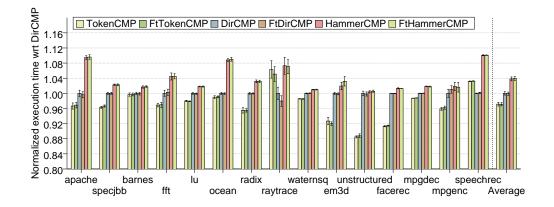

| 0.1 | Incremento en el tiempo de ejecución debida a las medidas de toleran-<br>cia a fallos en ausencia de fallos (resultados normalizados respecto a                                                                                                                                         | 10  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

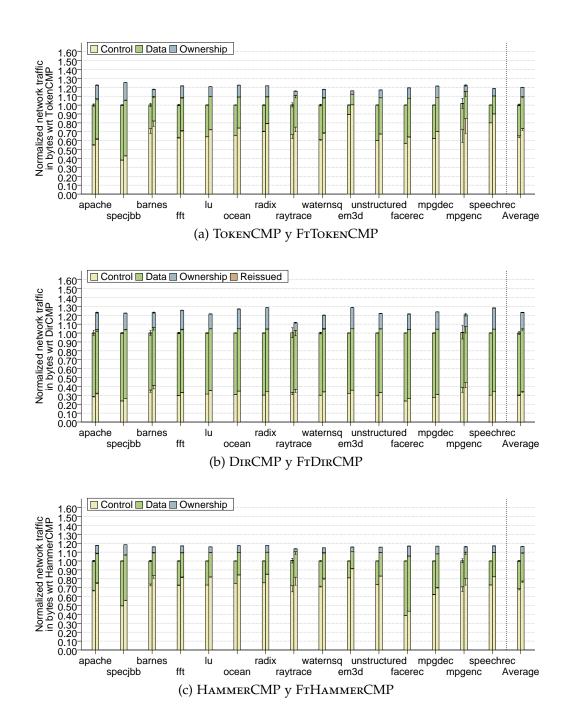

| 0.2 | DIRCMP)                                                                                                                                                                                                                                                                                 | 42  |

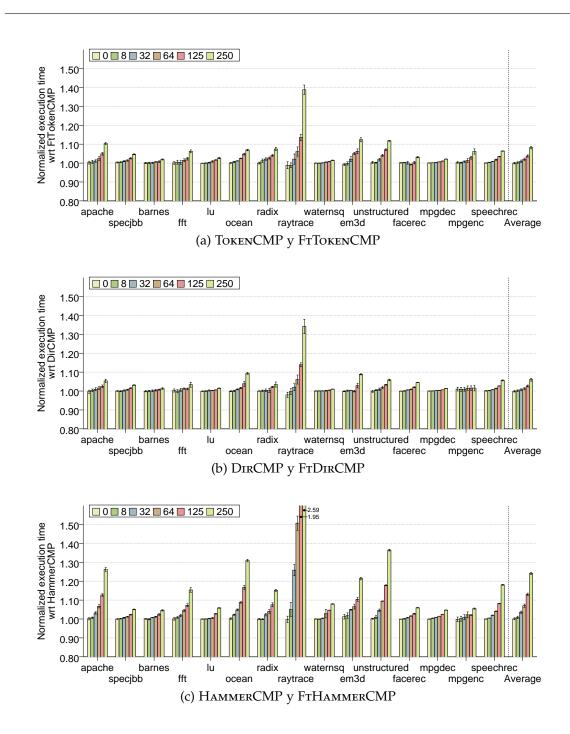

| 0.3 | zados respecto al protocolo no tolerante a fallos más similar<br>Degradación del rendimiento bajo diferentes tasas de fallos (en men-<br>sajes corrompidos por millón de mensajes que viajan por la red) para<br>cada protocolo tolerante a fallos respecto a su correspondiente proto- | 43  |

|     | colo base no tolerantes a fallos                                                                                                                                                                                                                                                        | 45  |

| 1.1 | Tiled Chip Multiprocessors                                                                                                                                                                                                                                                              | 51  |

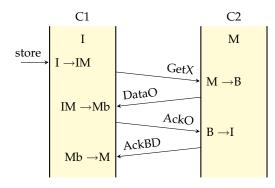

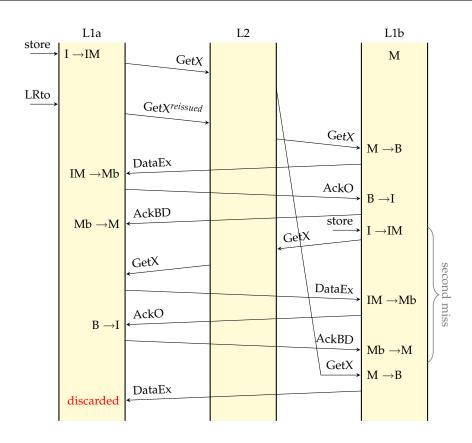

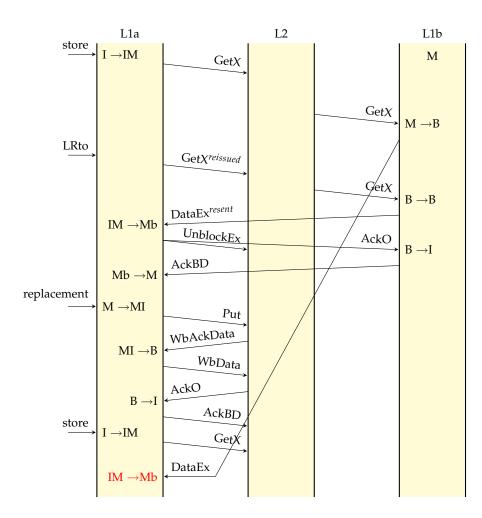

| 4.1 | Message exchange example of a cache-to-cache transfer using owned data loss avoidance in FtTokenCMP                                                                                                                                                                                     | 84  |

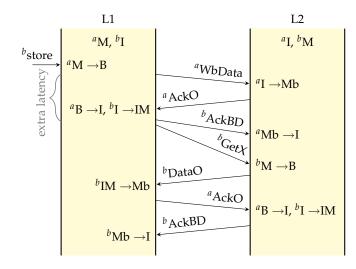

| 4.2 | Message exchange in FTTOKENCMP without backup buffer for a miss including the required previous write-back                                                                                                                                                                              | 86  |

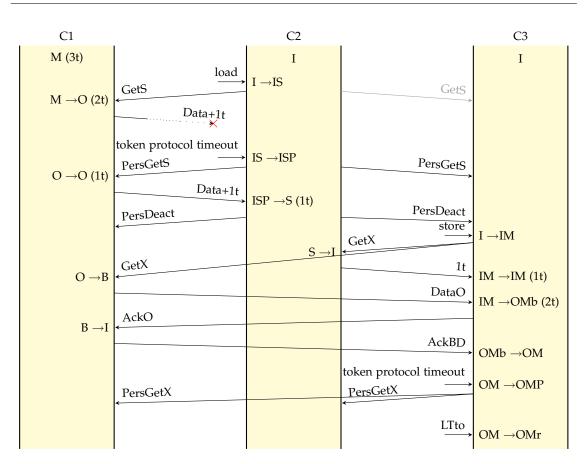

| 4.3 | Message exchange example of a token loss detected using the <i>lost token timeout</i>                                                                                                                                                                                                   | 90  |

| 4.4 | Message exchange in a token recreation process (used in this case to recover from the loss of an <i>ownership acknowledgment</i> )                                                                                                                                                      | 99  |

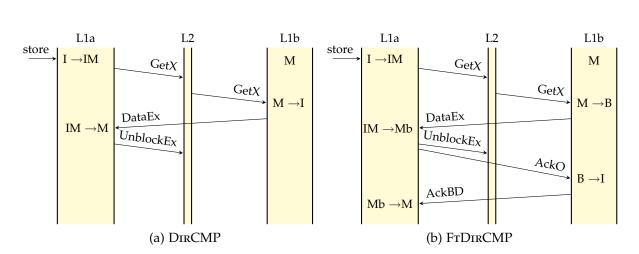

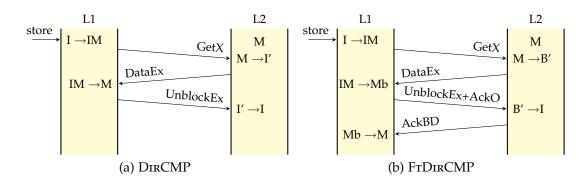

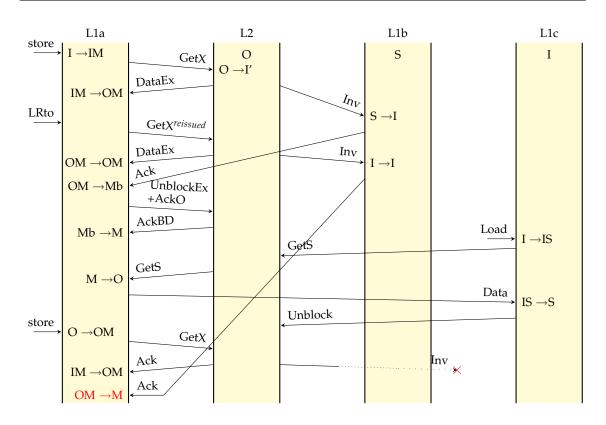

| 5.1 | Message exchange for a cache-to-cache write miss                                                                                                                                                                                                                                        | 110 |

| 5.2 | Message exchange for an L1 write miss that hits in L2                                                                                                                                                                                                                                   |     |

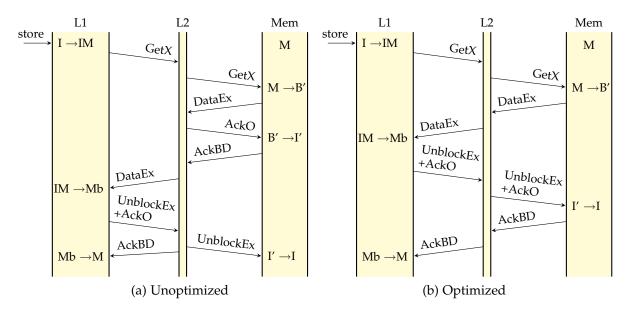

| 5.3 | L2 miss optimization of ownership transference                                                                                                                                                                                                                                          | 112 |

| 5.4 | Transaction where the <i>lost data timeout</i> detects data which has been                                                                                                                                                                                                              |     |

|     | wrongly discarded                                                                                                                                                                                                                                                                       | 118 |

| 5.5 | Transaction where request serial numbers are needed to avoid inco-<br>herency in a point-to-point ordered network                                                                                                                                                                       | 128 |

#### List of Figures

| 5.6  | Transaction where request serial numbers avoid using stale data in a point-to-point unordered network                                                                                                                                                             | 9 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

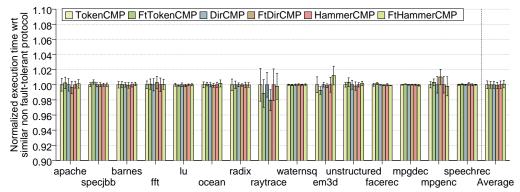

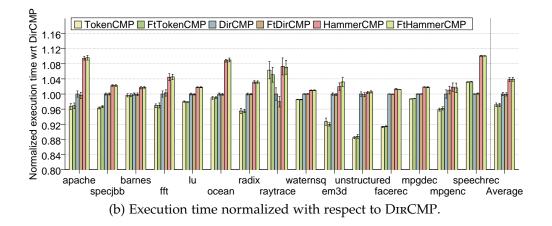

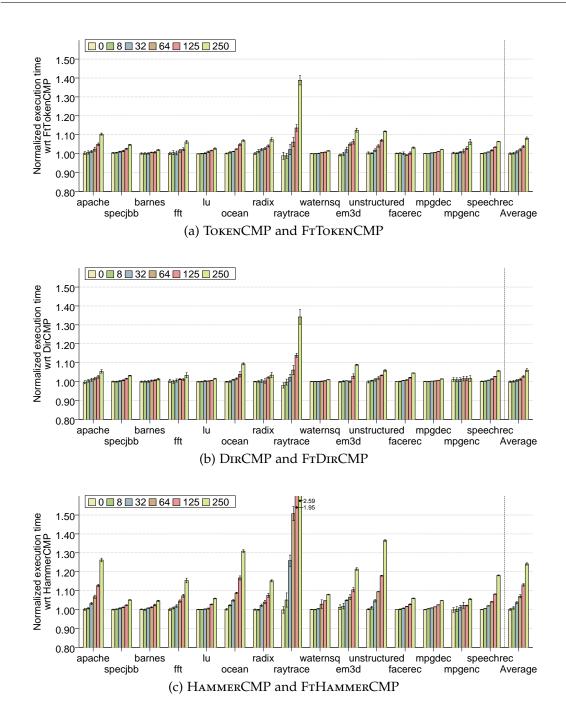

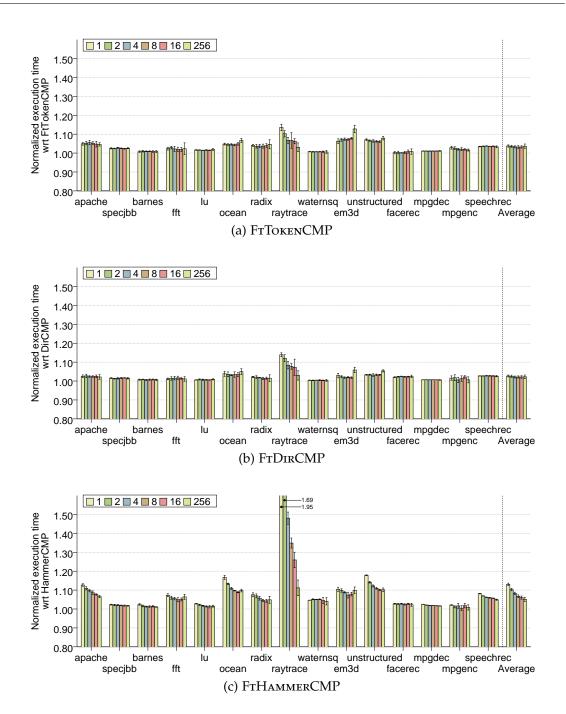

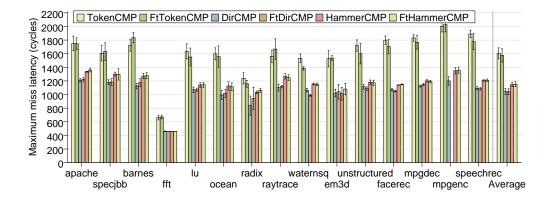

| 8.1  | Execution time overhead of the fault-tolerant cache coherence proto-<br>cols in absence of faults                                                                                                                                                                 | 2 |

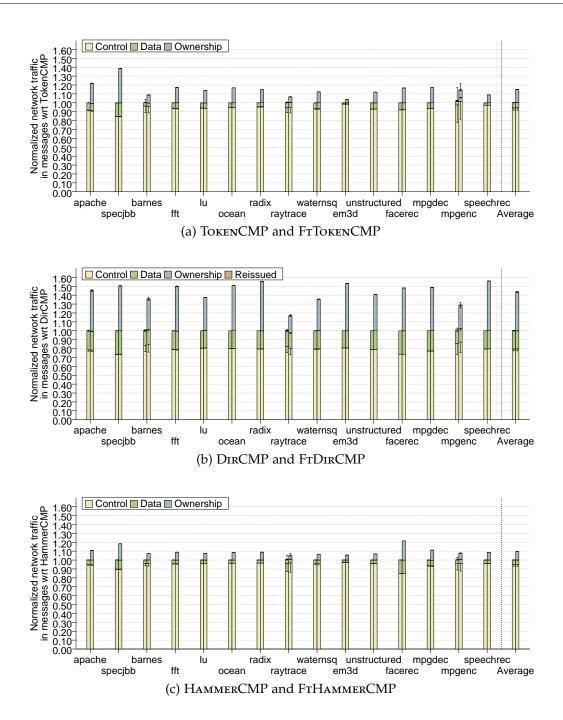

| 8.2  | Network overhead for each category of message in terms of number<br>of messages. Results are normalized with respect to the total number<br>of messages of the most similar non fault-tolerant protocol 154                                                       | 4 |

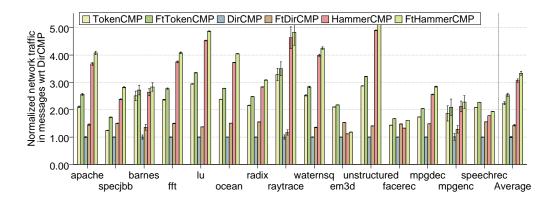

| 8.3  | Relative network traffic in terms of messages for each protocol nor-<br>malized with respect to DIRCMP                                                                                                                                                            | 5 |

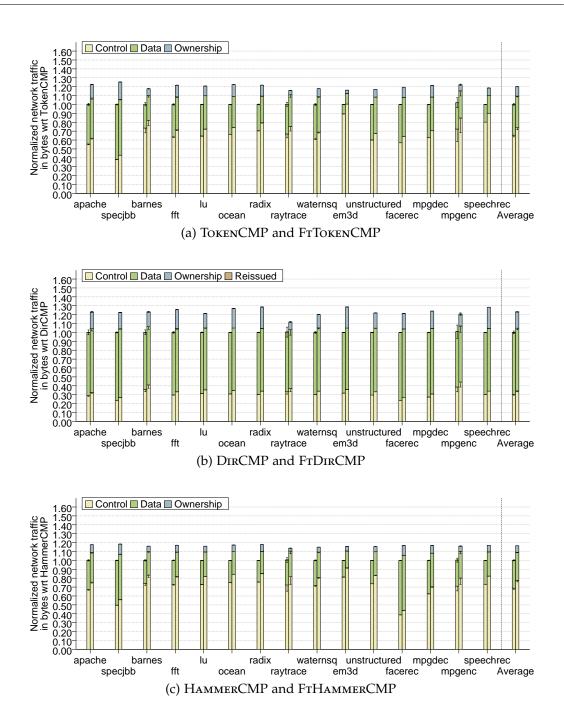

| 8.4  | Network overhead for each type of message in terms of number of bytes. Results are normalized with respect to the total number of bytes of the most similar non fault-tolerant protocol                                                                           | 6 |

| 8.5  | Performance degradation with different fault rates (in messages cor-<br>rupted per million of messages that travel through the network) for<br>each fault-tolerant protocol with respect to its non fault-tolerant coun-<br>terpart                               | 8 |

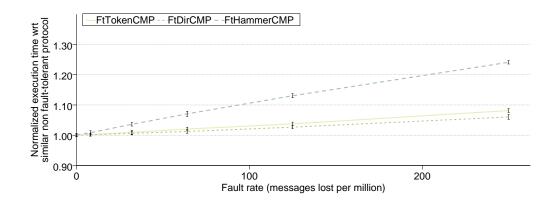

| 8.6  | Average performance degradation with different fault rates (in mes-<br>sages corrupted per million of messages that travel through the net-<br>work) for each fault-tolerant protocol with respect to its non fault-<br>tolerant counterpart                      | 9 |

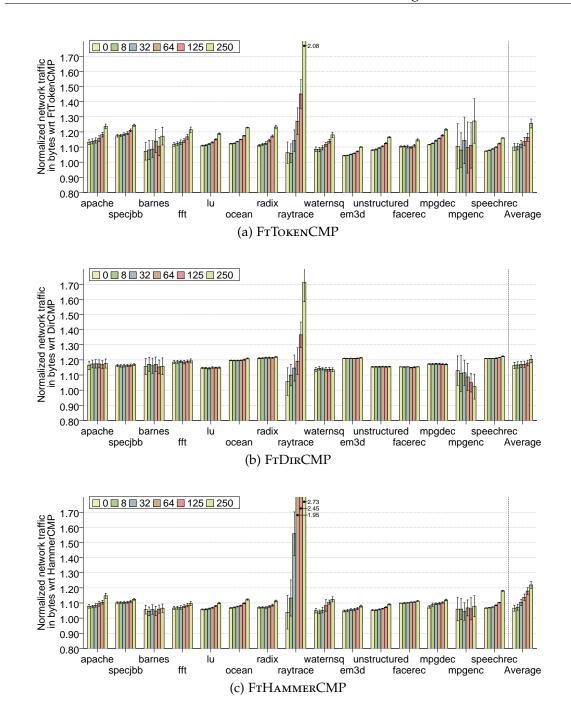

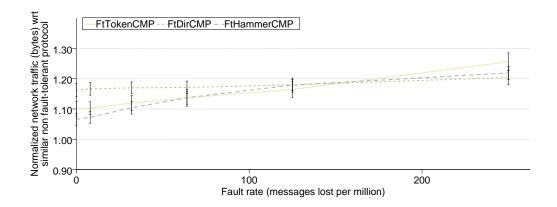

| 8.7  | Network usage increase with different fault rates (in messages cor-<br>rupted per million of messages that travel through the network) for<br>each fault-tolerant protocol with respect to its non fault-tolerant coun-<br>terpart                                | 1 |

| 8.8  | Average network usage increase with different fault rates (in messages corrupted per million of messages that travel through the network) for each fault-tolerant protocol with respect to its non fault-tolerant counterpart                                     | 2 |

| 8.9  | Performance degradation with burst faults of several lengths for each fault-tolerant protocol with respect to its non fault-tolerant counterpart. The total fault rate is fixed to 125 corrupted messages per million of messages that travel through the network | 4 |

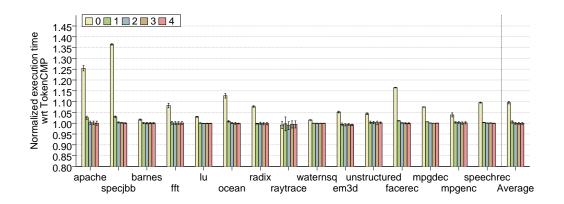

| 8.10 | Execution time of FTTOKENCMP normalized with respect to To-<br>KENCMP when no faults occur and using different backup buffer<br>sizes                                                                                                                             |   |

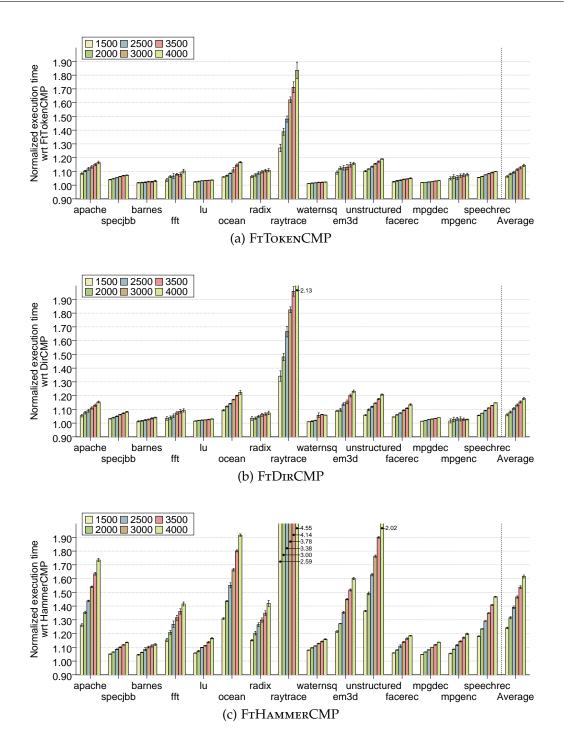

| 8.11 | Performance degradation of the fault-tolerant protocols with a con-<br>stant fault rate of 250 lost messages per million of messages travelling |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|      | through the network and with different values for the fault detection                                                                           |

|      | timeouts, using the same value for all the timeouts of each protocol . 168                                                                      |

| 8.12 | Maximum miss latency (in cycles) of each cache coherence protocol                                                                               |

|      | without faults                                                                                                                                  |

| 8.13 | Required request serial number bits to be able to discard every old<br>response to a reissued message when faults occur. In the fault-free      |

|      | case, no bits are required at all in any of our tests                                                                                           |

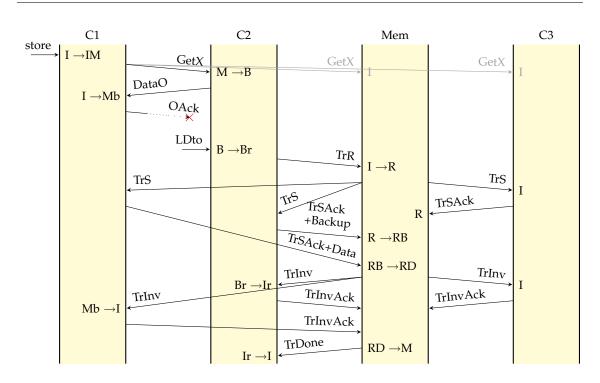

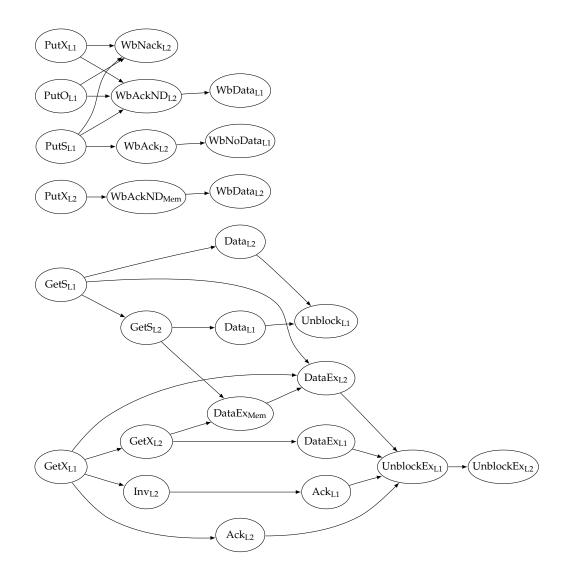

| C.1  | Message dependency chains for the DIRCMP protocol                                                                                               |

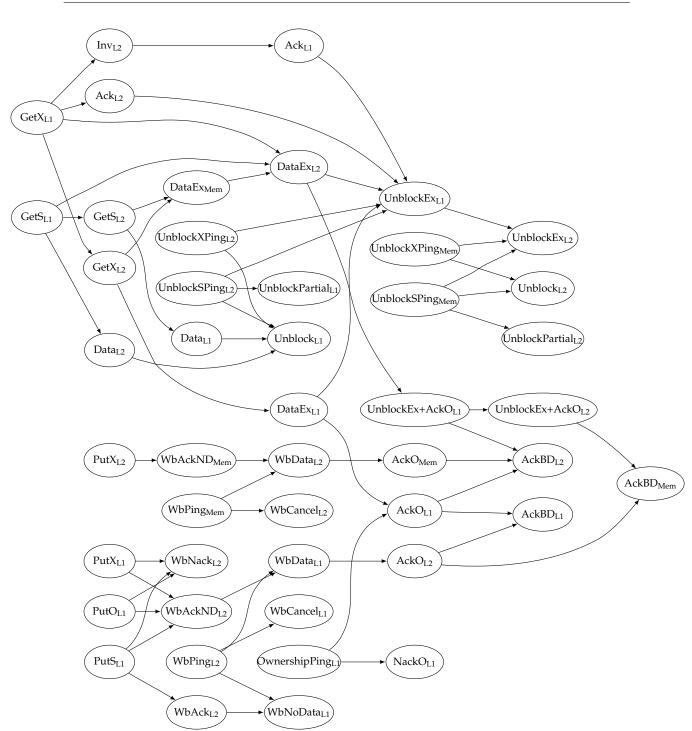

| C.2  | Message dependency chains for the FTDIRCMP protocol                                                                                             |

# **List of Tables**

| 0.1 | Resumen de <i>timeouts</i> usados en FtTokenCMP                        |

|-----|------------------------------------------------------------------------|

| 0.2 | Resumen de <i>timeouts</i> usados en FTDIRCMP                          |

| 0.3 | Características de las arquitecturas simuladas 41                      |

| 0.4 | Benchmarks y tamaños de problema usados en las simulaciones 42         |

| 4.1 | Summary of the problems caused by loss of messages in TOKENCMP . 76    |

| 4.2 | Summary of timeouts used in FtTokenCMP 82                              |

| 4.3 | Summary of the problems caused by loss of messages in FTTOKENCMP       |

|     | and the detection and recovery mechanisms employed 83                  |

| 5.1 | Message types used by DIRCMP and the effect of losing them 103         |

| 5.2 | Additional message types used by FTDIRCMP                              |

| 5.3 | Summary of timeouts used in FTDIRCMP                                   |

| 5.4 | Timeout which detects the loss of each type of message in FTDIRCMP 106 |

| 6.1 | Summary of timeouts used in FTHAMMERCMP                                |

| 7.1 | Characteristics of simulated architectures                             |

| 7.2 | Benchmarks and input sizes used in the simulations                     |

| A.1 | Correspondence of token counting states with MOESI states 185          |

| B.1 | Message types used by DIRCMP                                           |

# List of Acronyms

- **BER:** Backward Error Recovery.

- **CARER:** Cache Aided Rollback Error Recovery.

- **CCA:** Core Cannibalization Architecture.

- CMP: Chip Multiprocessor.

- **CRC:** Cyclic Redundancy Code.

- **DCT:** Discrete Cosine Transform.

- DMR: Dual Modular Redundancy.

- **DRSM-L:** Distributed Recoverable Shared Memory with Logs.

- **DUE:** Detected but Unrecoverable Error.

- **ECC:** Error Correcting Code.

- **EDC:** Error Detecting Code.

- **EMI:** Electromagnetic Interference.

- FER: Forward Error Recovery.

- FFT: Fast Fourier Transform.

- FIFO: First In First Out.

- **GEMS:** General Execution-driven Multiprocessor Simulator.

- **HTML:** Hypertext Markup Language.

HTTP: Hypertext Transfer Protocol.

**IDCT:** Inverse Discrete Cosine Transform.

- ILP: Instruction Level Parallelism.

- LPC: Low Power Codes.

- M-CMP: Multiple CMP.

- **MOESI:** Modified Owned Exclusive Shared Invalid (set of cache coherence states).

- **MPEG:** Moving Picture Experts Group.

- MSHR: Miss Status Holding Register.

- **MSSG:** MPEG Software Simulation Group.

- MTTR: Mean Time To Recover.

- **RSM:** Recoverable Shared Memory.

**SDC:** Silent Data Corruption.

- **SECDED:** Single Error Correction / Double Error Detection.

- **SLICC:** Specification Language Including Cache Coherence.

- SMP: Symmetric Multiprocessors.

- **SMT:** Simultaneous Multithread.

- TCP: Transmission Control Protocol.

- TLP: Thread Level Parallelism.

- TMR: Triple Modular Redundancy.

- **TRUSS:** Total Reliability Using Scalable Servers.

- **VLSI:** Very Large Scale of Integration.

### Resumen

### Introducción

La mejora en la tecnología de semiconductores está haciendo posible que cada vez se puedan incluir más transistores en un solo chip. Los arquitectos de computadores deben decidir de qué forma usar estos transistores para obtener el mejor rendimiento posible. Tradicionalmente, se viene considerando que la faceta más importante del rendimiento es la velocidad de ejecución de las aplicaciones que finalmente se ejecutan en esos chips.

Sin embargo, el rendimiento no puede ser entendido solo desde el punto de vista de la velocidad de ejecución. Otros factores como la dificultad para programar el procesador resultante o su consumo energético también son importantes. El peso relativo de cada variable depende del uso final del chip.

Uno de los aspectos del rendimiento de un sistema es la fiabilidad del mismo. La misma tendencia de miniaturización de los transistores que permite disponer de mayor número de ellos, también hace que la fiabilidad de los mismos disminuya. Debido a esto, es necesario aplicar técnicas de tolerancia a fallos a varios niveles del sistema. Hasta hace poco, estas técnicas eran importantes solo en determinadas aplicaciones críticas. Sin embargo, actualmente son necesarias para todo tipo de sistemas para mantener niveles de fiabilidad aceptables.

Los fallos cuya frecuencia está aumentando más rápidamente debido a las tendencias tecnológicas son los fallos transitorios. Cuando ocurre un fallo transitorio, un componente produce una salida incorrecta pero continua funcionando correctamente después del fallo [87,89].

Uno de los componentes de un CMP (*Chip Multiprocessor* [11, 50]) que se verá afectado por los fallos transitorios mencionados anteriormente es la red de interconexión. Ésta se usa para permitir el intercambio de los mensajes del

#### Resumen

protocolo de coherencia de caché [27] entre procesadores, cachés y memorias; y su rendimiento es clave para el rendimiento general del sistema.

La red de interconexión es especialmente vulnerable a los fallos transitorios debido a que ocupa una porción importante de la superficie del chip, lo que aumenta la probabilidad de impacto de partículas. Además, está construida usando hilos más largos en promedio que el resto de componentes, lo que la hace más propensa a acoplamiento (*crosstalk*) e incrementa aún más las probabilidades de fallos transitorios [34]. Los fallos transitorios en la red de interconexión provocan la corrupción de los mensajes del protocolo de coherencia de caché, lo que en última instancia causa interbloqueos o corrupción de datos no detectada.

Una forma de solucionar los problemas causados por los fallos transitorios en la red de interconexión es construir una red de interconexión tolerante a fallos. Hay múltiples propuestas de redes de interconexión tolerantes a fallos que se mencionan en la sección de trabajo relacionado de esta tesis.

A diferencia de otros trabajos, en esta tesis se propone tratar con los fallos transitorios en la red de interconexión a nivel del protocolo de coherencia de caché, en lugar de a nivel de la propia red. Este enfoque tiene las siguientes ventajas:

- El protocolo de coherencia tiene más información sobre el significado de los mensajes y sobre los efectos de perder cada mensaje. De esta forma, se pueden utilizar opciones más inteligentes para obtener el mismo nivel o mayor de tolerancia a fallos con una sobrecarga menor. Por su parte, las medidas de tolerancia a fallos a nivel de la red de interconexión tienen que tratar a todos los mensajes por igual.

- La implementación de medidas de tolerancia a fallos a nivel de la red de interconexión limita la capacidad de maniobra del diseñador de la red de interconexión para optimizar agresivamente otros aspectos del rendimiento de la misma.

- Como se mostrará más adelante, un protocolo de coherencia tolerante a fallos se comporta la mayoría del tiempo casi igual que un protocolo de coherencia convencional. En ausencia de fallos, solo se observan diferencias cuando un mensaje crítico necesita ser transmitido.

Por contra, implementar las medidas de tolerancia a fallos a nivel del protocolo de coherencia de caché también tiene sus desventajas. La mayor desventaja es tener que modificar el propio protocolo de coherencia, cuyo rendimiento también

es clave para el rendimiento general del sistema y cuyo diseño suele considerarse complejo. En esta tesis mostramos que el aumento de complejidad es asumible y la sobrecarga en el rendimiento es pequeña.

En nuestro modelo de fallos, suponemos que, desde el punto de vista del protocolo de coherencia, la red de interconexión entrega correctamente un mensaje o bien no lo entrega en absoluto. Esto es fácil de conseguir añadiendo códigos de detección de errores [58,89] que sean comprobados a la llegada del mensaje, y descartando los mensajes que se detecten corruptos. Los mensajes inesperados se supone que han sido mal enrutados y se descartan también.

Aunque en esta tesis suponemos que los mensajes son descartados debido a errores transitorios, las mismas técnicas se podrían utilizar si los mensajes se descartasen por cualquier otra razón como, por ejemplo, falta de espacio en buffers de la red de interconexión. Esta propiedad puede ser útil para los diseñadores de red.

En esta tesis se hacen las siguientes aportaciones:

- Se identifican los problemas causados por una red de interconexión no fiable en CMPs con coherencia de caché.

- Se proponen modificaciones a los protocolos de coherencia de caché que es más probable que se usen en *tiled CMPs* [127, 128, 14] para soportar el descarte de algunos mensajes por la red de interconexión sin añadir excesiva sobrecarga.

- Un protocolo de coherencia de caché que extiende un protocolo basado en *tokens* con medidas de tolerancia a fallos, y modificaciones a las reglas genéricas de conteo de *tokens* para asegurar la transferencia fiables de datos y propiedad de los datos.

- Un protocolo de coherencia de caché que extiende un protocolo de coherencia basado en directorio con medidas de tolerancia a fallos.

- Un protocolo de coherencia de caché que extiendexs un protocolo de coherencia tipo *snoopy* basado en broadcast con medidas de tolerancia a fallos.

- Dado que nuestros protocolos de coherencia imponen menos requerimientos a la red de interconexión que otros, esperamos que sean útiles para simplificar el diseño de la red y permitir la aplicación de técnicas agresivas para mejorar el rendimiento.

Se evalúan los protocolos tolerantes a fallos usando simulación del sistema completo para comprobar su efectividad y para medir la sobrecarga introducida en ausencia de fallos y la degradación del rendimiento bajo distintas tasas de fallo.

# Premisas generales y requerimientos para los protocolos de coherencia tolerantes a fallos

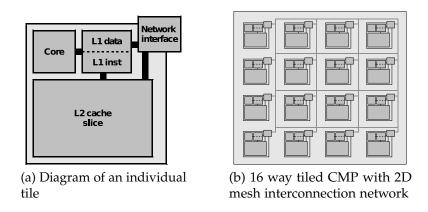

Para desarrollar y evaluar las propuestas de esta tesis, partimos de una arquitectura basada en tiled CMPs [127, 128, 14]. La gran cantidad de transistores disponibles en un solo chip ha obligado a replantearse cuál es la mejor forma de organizarlos. Mientras que hasta hace pocos años se trataba de obtener el mayor rendimiento posible aumentando la frecuencia del circuito y explotando el paralelismo a nivel de instrucción (ILP), los límites físicos y la gran complejidad necesaria para obtener pequeñas mejoras hacen estas vías poco atractivas actualmente. Hasta la fecha, la forma más práctica que se ha propuesto para hacer uso de estos transistores es construir multiprocesadores en un solo chip (CMPs) que exploten el paralelismo a nivel de hilo (TLP) además, o incluso en lugar, de a nivel de instrucción. Para reducir aún más la complejidad de los CMPs, los tiled CMPs se construyen replicando tiles (baldosas) idénticos entre sí y conectados mediante una red de interconexión punto a punto. Cada tile está formado por un núcleo de procesador, una caché privada, una parte de una caché compartida y un interfaz de red. Los tiled CMPs son una arquitectura muy probable para futuros diseños de chips con gran número de procesadores.

Para la evaluación, se asume una red de interconexión punto a punto con topología de malla y enrutamiento determinista, aunque los protocolos en sí no requieren ninguna característica concreta de la red. En particular, no se hace ninguna suposición sobre el orden de entrega de los mensajes.

Aunque en esta tesis se asume la arquitectura anteriormente descrita como base, las propuestas que se presentan son también aplicables a cualquier tipo de CMP con red de interconexión punto a punto e incluso para sistemas multiprocesadores en varios chips.

Nuestras propuestas presuponen que la memoria y las cachés están protegidas mediante ECC (*Error Correction Codes*) u otros medios. Es decir, los datos solo se tienen que proteger mientras viajan por la red.

Nuestro objetivo es diseñar protocolos de coherencia de caché que garanticen la correcta ejecución de aplicaciones paralelas incluso sobre una red de interconexión no fiable, sin tener que realizar nunca *rollback* debido a errores en dicha red. Así mismo, evitaremos la introducción generalizada de mensajes de reconocimiento punto a punto, para evitar incrementar innecesariamente la latencia de las transacciones de coherencia, el tráfico de la red, o el tamaño de los buffers.

Una red de interconexión no fiable causa una serie de problemas en un *tiled CMP*: corrupción silenciosa de datos, violación no detectada de la coherencia de memoria, interbloqueos (*deadlock*), errores detectables pero no recuperables (interbloqueos, corrupción o pérdida de datos) o degradación del rendimiento.

Para evitar los problemas mencionados anteriormente, un protocolo de coherencia de caché tolerante a fallos debe ofrecer las siguientes características:

- **Evitar corrupción de datos:** El sistema debe ser capaz de detectar mensajes que han sido corrompidos y descartarlos. Para ello, se pueden utilizar códigos de detección de errores (EDC). Algunos sistemas ya usan EDC en los mensajes de la red de interconexión para evitar la corrupción no detectada de datos aunque no dispongan de otras medidas de tolerancia a fallos en el protocolo de coherencia.

- **Evitar pérdida de datos:** Debido a que los mensajes pueden ser descartados, es necesario que se evite enviar datos a través de la red de interconexión sin conservar al menos una copia de los mismos para que puedan ser recuperados en caso necesario.

- **Evitar incoherencias:** Un protocolo de coherencia tolerante a fallos necesita asegurar que la coherencia de caché no se puede llegar a violar debido a que un mensaje no llega a su destino. En particular, los mensajes de invalidación deben requerir el envío de mensajes de reconocimiento, ya sea al peticionario o al directorio. Estos mensajes de reconocimiento ya son necesarios en la mayoría de los protocolos de coherencia para evitar condiciones de carrera.

- **Detectar y recuperar interbloqueos:** Cuando un mensaje de coherencia es descartado, esto provoca en la mayoría de las ocasiones un interbloqueo. Es por tanto necesario incluir mecanismos de detección y resolución de interbloqueos.

Para poder ser útil, en ausencia de fallos, un protocolo de coherencia tolerante a fallos debe, además de incluir las características arriba mencionadas, ofrecer un rendimiento muy similar al de un protocolo de coherencia no tolerante a fallos que usara una red de interconexión fiable.

#### Resumen

### Diseño de un protocolo de coherencia de caché basado en *tokens* tolerante a fallos